什么是DDR3阻抗匹配

DDR3为双倍数据速率同步动态随机存取存储器(SDRAM)的代表之一,被广泛运用于当前计算机体系结构中。而阻抗匹配则是维护DDR3信号稳定、可靠传输的基石。在DDR3内存模组设计里,信号线的阻抗匹配成为了关键性任务,同时也牵涉到了信号传输速度、能源消耗及电磁干扰等议题。

通常情况下,DDR3内部分为多条信号线,包括数据线、地址线、控制线等。但值得注意的是,这些信号在线传输过程中易受阻抗不匹配的影响,且若此问题严重的话,将可能导致传输速度下降、功耗增加甚至引发数据错误等诸多问题。因此,正确实施DDR3阻抗匹配策略显得尤为必要,以保障内存系统高效稳定地运行。

为什么需要进行DDR3阻抗匹配

在现代计算机体系架构中,DDR3内存模组发挥至关重要之作用。其性能及稳定度均受其影响。为了保障数据精确且无延迟的传输,必须对DDR3内部分配线路的阻抗进行精准调节。此为何需实施DDR3阻抗调谐原因所在。

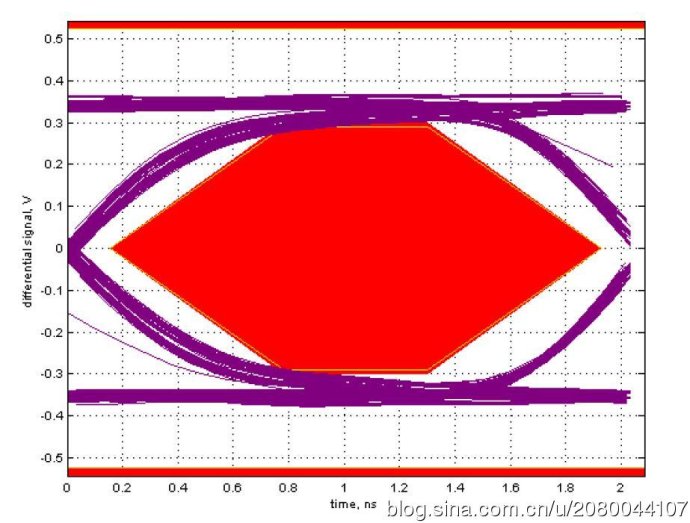

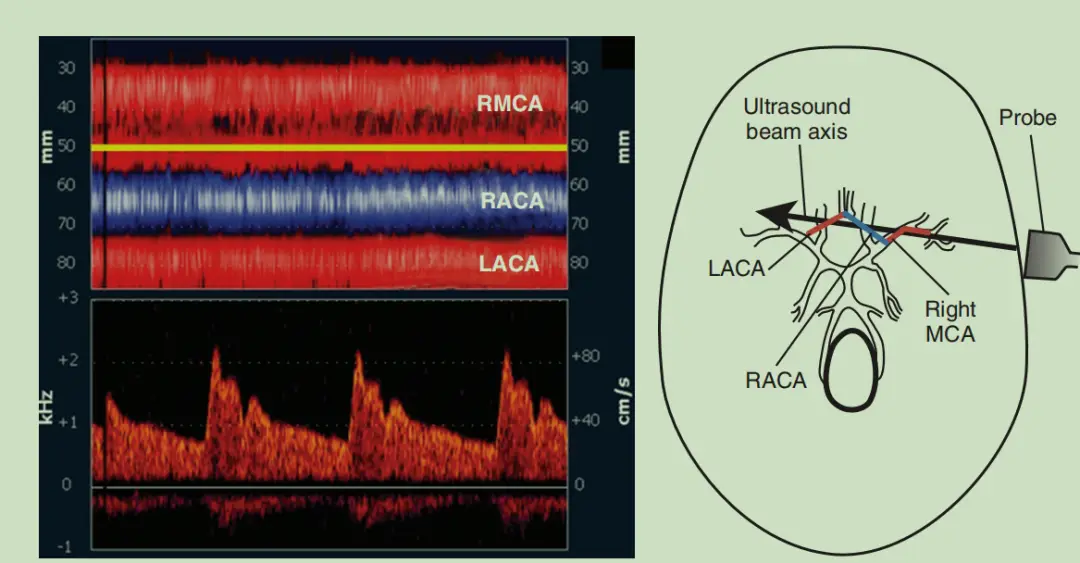

首先,DDR3内存模块因操作频次高等特性,对信号传输质量有较高需求。如信号线上出现显著反射与串扰状况,将导致数据传输误差提升,进而影响系统整体表现。其次,当以高频率执行任务时,信号波形上升沿及下降沿时段甚为短暂,从而对信号完整性的要求相应提升。借助DDR3阻抗匹配手段,可有效降低反射与串扰,提高信号完整性。

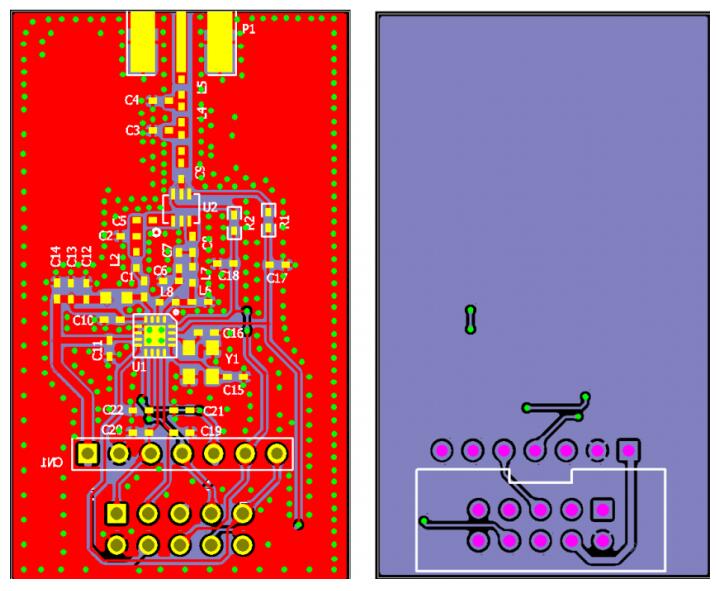

多通道设计需进行阻抗匹配以保持通道同步与稳定。故而,设计DDR3内存模块时应充分考虑信号线长度、层间及板层堆叠方式,相应调整阻抗以满足需求。

如何进行DDR3阻抗匹配

理想情况下,实现高效的DDR3阻抗匹配在设计中至关重要且复杂。在此过程中,需准确理解如下几方面的定义:驱动器、传输线路、终端端口及接收端。

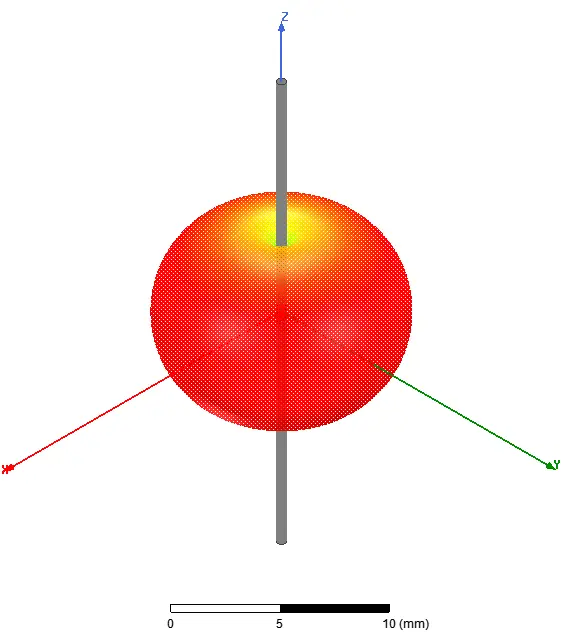

在DDR3布线设计过程中,需着重关注驱动器端的输出电阻与传输线路特性阻抗的适配性。通常情况下,两者匹配可实现反射最小化及提升信号的完整性。此外,在末端端口设立适当的终端电路亦是必要的举措,以消弭反射波影响,确保信号品质达至最优水平。

多通道设计需关注各通道间交互影响与相位误差问题,可通过精密布局、甄选最佳终端电路及调节驱动端输出电阻等方式,成功化解通道间的阻抗匹配难关。

在实施DDR3阻抗匹配工程中,必须整体考虑布线间距、线路层级结构、驱动端的输出阻抗与元器件选择等多种影响因素,并辅以模拟软件来检验和完善方案。

常见问题及解决方法

在实际应用进程中,常会面临一系列熟悉的难题,从而影响到DDR3电阻匹配的效果。譬如,布局设计阶段的信号线长度不均引发了相位差;或驱动器输出大电流过猛导致极端的反射。

对于诸如此类的常见问题,我们可实施部分对策以缓解。譬如,借助分层布局策略,将各信号线的长度保持契合,以便缩小其相位差;或通过微调驱动端输出电流的强度,降低反射波峰值,以此提升阻抗匹配性能。

实践中,借助仿真技术可准确验证并精简DDR3的内部线路设计,提升其稳定性与可靠性。

未来发展趋势

在计算机科技日益精进之际,DDR3内部线路技术的需求亦日益提升。未来发展趋向主要涉及以下几点:

首当其冲的便是密集型集成的趋势。鉴于芯片制造技术持续创新,集成度必将大幅提高,因此,DDR3原件的内部布线亦需走向紧密集成的更高级别。

未来计算需求将体现在对处理器功耗及频率的进一步提高上,而这对于DDR3模块内部布线技术提出了新的挑战与机遇。以高效能为核心,兼顾降低能耗与提升工作频率成为重要研究方向。

展望未来,DDR3内部布线技术将逐步迈入智能化自适应阶段,利用智能算法进行自动调整与优化布线参数,满足在各种不同运行环境中的调度需要。

结语

总的来说,DDR3内存架构内阻抗匹配在实践操作过程中显得颇为关键且复杂。通过精心设定布局与选择适用端接电路,或是利用仿真辅助进行优化验证,都能有针对性地提升系统稳定性及可靠性,进而保障数据信号在传输时能够实现优质效果。

期望本篇文章能使您更深入了解DDR3阻抗匹配技术,从而助您在实际操作中实现更优质的效果。同时,我们热忱期待您的宝贵意见和相互探讨,以共促实践中的成长与精进!