身处数字化时代,DDR3内存成为了现代数字系统设计不可或缺的组件。同样,Xilinx作为行业翘楚的可编程逻辑器件提供商,他们的FPGA芯片被广泛运用于各个领域。因此,掌握Xilinx DDR3设计教程对于广大数字系统工程师尤显紧迫与必要。接下来,我们将针对这一课题进行深入研究,由浅入深、从理论至实践,为您全方位揭示并理解这一核心技术。

1. DDR3内存简介

DDRO3内存,精称双倍数据传输率同步动态随机存取存储器,极速、大容量与低能耗的特性使其应用范围覆盖数字电子设备、通信技术以及嵌入式系统设计等多个领域。DDR3内存拥有几百至1GHz的工作频率,大作家满足现代高性能系统对于内存带宽的高要求。

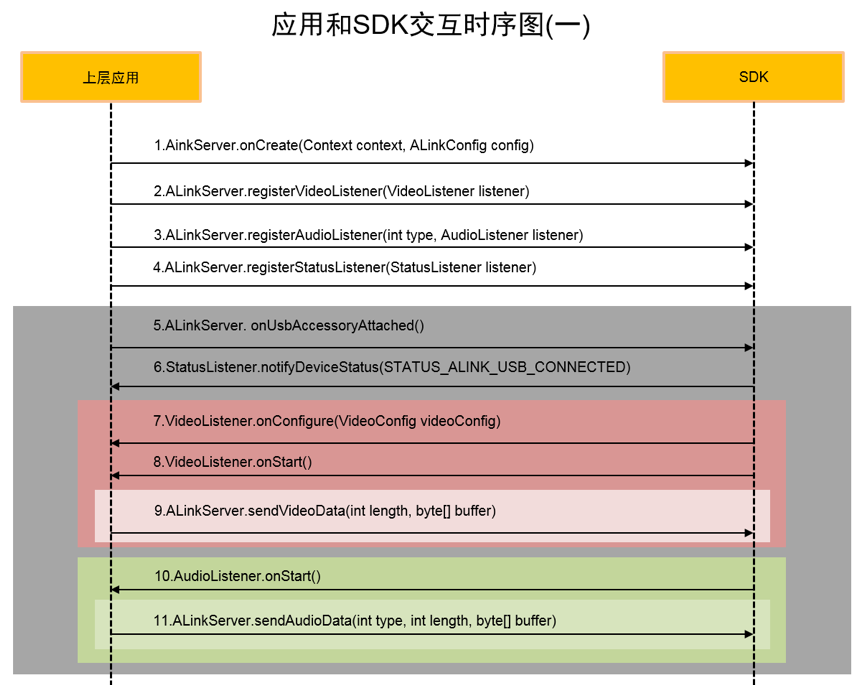

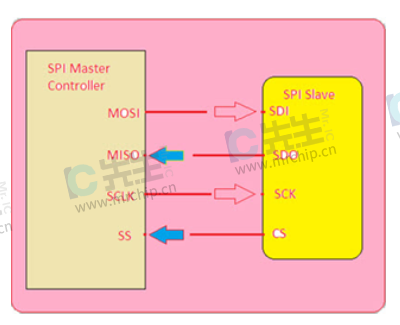

DDR3存储与处理器间的信息传递主要依托总线完成,故而在流程设计阶段需对时序、布局和信号完整性妥善考量。Xilinx FPGA作为这两者间的接口环节,其设计尤为关键,须确保数据传输的可靠性。

2. Xilinx FPGA概述

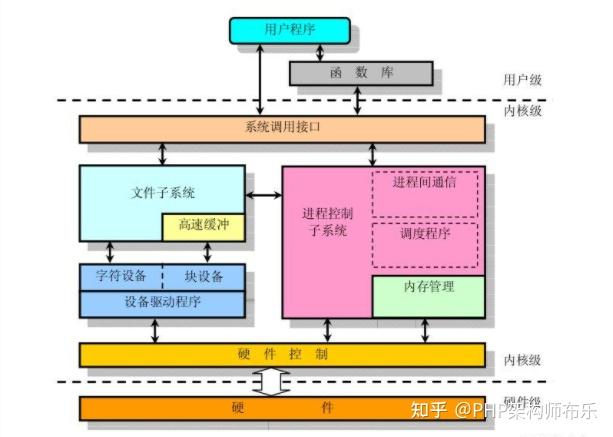

Xilinx FPGA乃高度灵活的可编程序逻辑设备,具备卓越集成度及优良性能,其配置选项改变多样的数字电路功能,适用于数字信号处理、信息通讯以及图像处理等应用范畴。现今,Xilinx已然成为FPGA行业翘楚,凭借多样化的开发工具及其丰富的IP核藏品,为使用者奠定坚实基础。

在DDR3系统设计过程中,Xilinx FPGA起到了至关重要的作用。利用其内部资源及外部接口的合理调配,能有效地构建与DDR3存储器的高速通信通道。另一方面,Xilinx FPGA所拥有的出色时序控制功能和充裕的IO资源使之成为DDR3接口控制及数据传输的理想选择。

3. DDR3接口电路设计

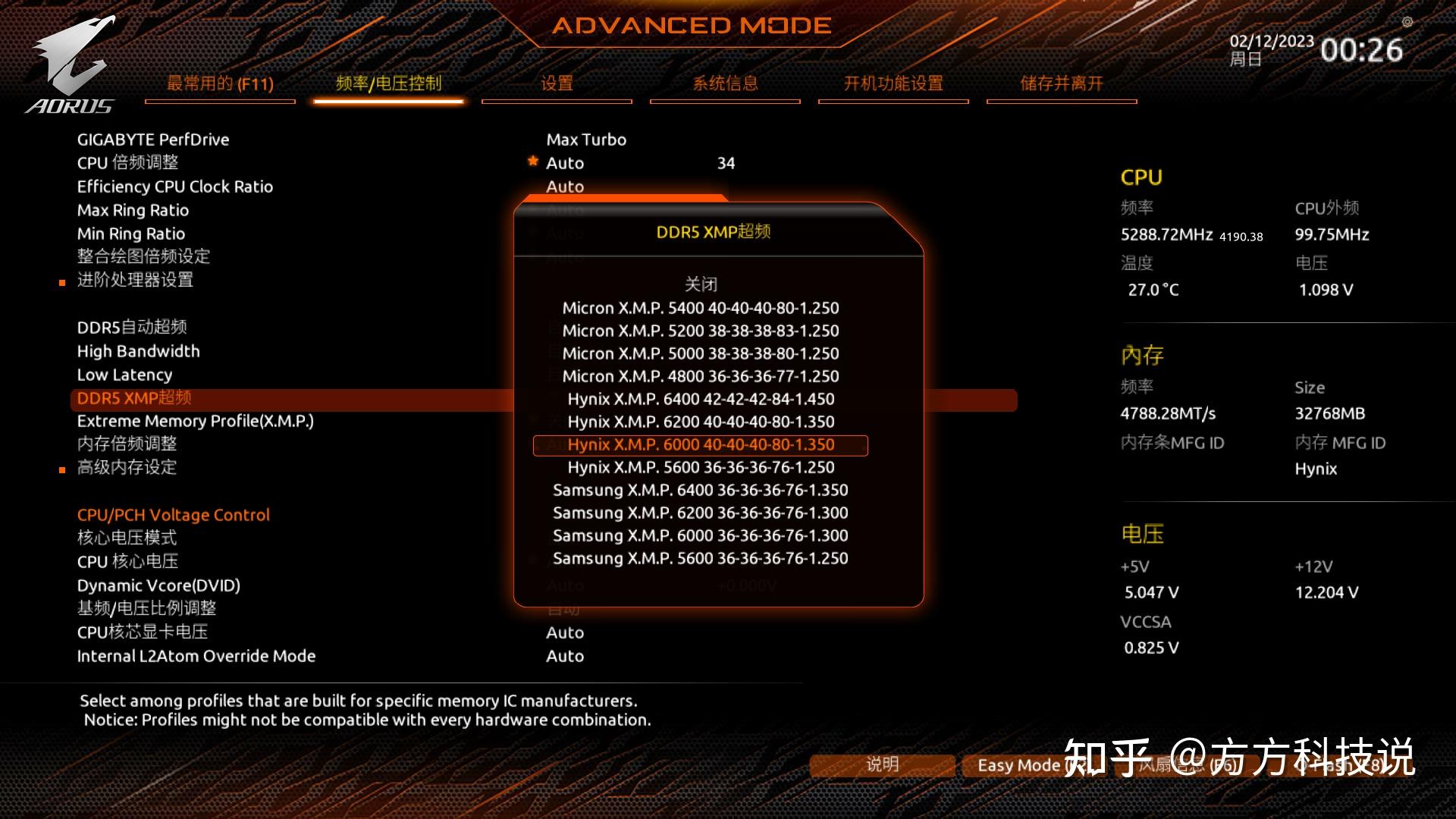

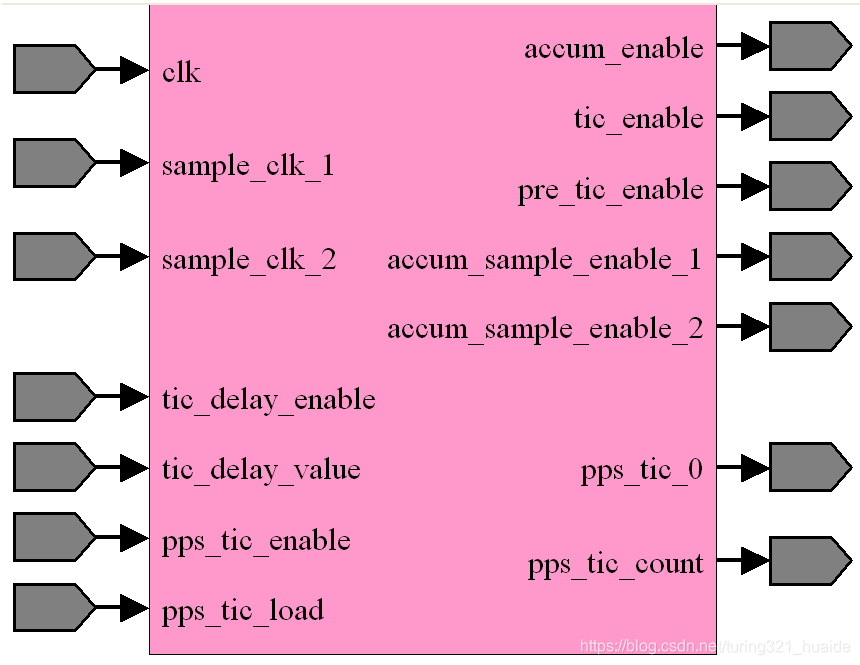

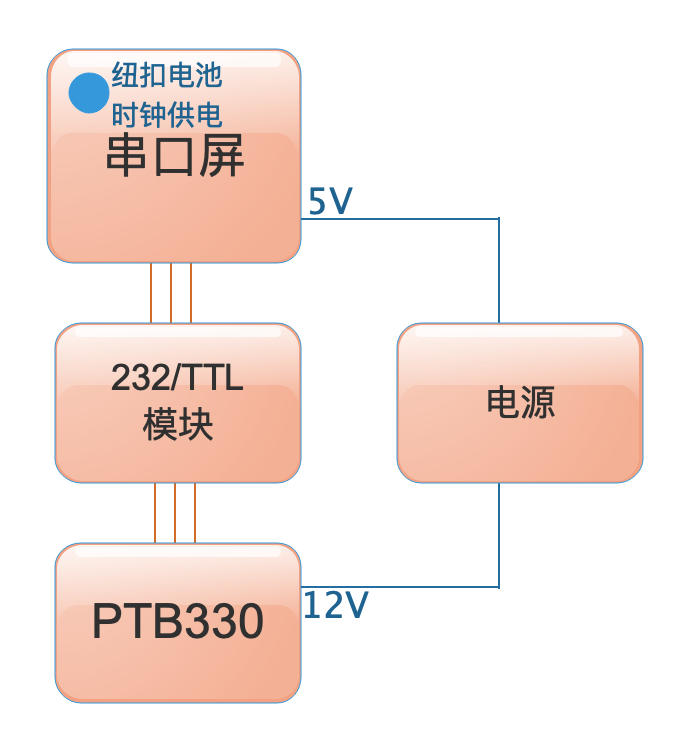

在Xilinx FPGA中实现DDR3接口设计过程中,需重点关注时序匹配、布局布线与信号完整性的问题。首先,须依据DDR3规格书制定相应时序参数;其次,利用FPGA内置时钟模块生成与时序参数相匹配的时钟信号。此外,在PCB板布局规划方面,得注重差分线长度匹配以及阻抗调节等精细操作。

对于XILINX FPGA的设计,需善用其PLL与MMCM等资源进行时钟管理与数据同步。此外,正确配置BRAM资源以提升数据缓存及预取效能,进而提高数据传输速率。

4. Xilinx Vivado工具使用

Vivado是赛灵思公司精心研发的综合性FPGA开发工具套件,覆盖了整个开发周期,具体包括综合、实现和调试三大关键步骤。在DDR3设计实施阶段,该套件能协助使用者顺利地从RTL设计直至BIT文件产出的完整过程。

Vivado工具可实施包括逻辑综合、约束编辑以及时序分析在内的操作,以智能辅助用户验证其设计是否满足严格的时间要求,并随即生成最终配置文件载入至特定FPGA芯片中。另外,此举还为调试环节增添了便利性,借助Vivado所能提供的丰富仿真功能,用户得以方便、高效地对设计进行验证与调试。

5.时序约束设置

在赛灵思DDR3设计流程里,合理制定和实施时序规定至关重要。这招能引领合成程序做出优化调整,从而使产生的电路具备上述的时间压力。此外,DDR3接口部分必须有精确设定的阅读和写作时间,时钟延迟等限定也需考虑在内。

借助Vivado工具能便捷设定时序要求,实现对时序约束文件的管理与分析。合理设定可有效避免因时序问题引起的工设失误或性能下滑现象。

6.信号完整性分析

在设计DDR3接口时,信号完整性显得尤为关键。因为高速信号传输常伴随着反射与串扰等潜在干扰因素,为保证信号质量,进行细致全面的分析及仿真验证至关重要。在赛灵思FPGA设计过程中,应自始至终将信号完整性纳入考量,特别是PCB布局规划阶段以及引脚分配环节。

直接运用于Signal Integrity Wizard的视觉模型与分析技术可深度剖析并寻觅出DDR3接口可能存在的问题及其具体因素,进而有针对性地加以解决。同时,借助模拟实践和实验论证,我们能自主评价各种配置方案对信号质量的效应效果,并优化工程设计流程,以保证整个系统的绝对稳定。

7.系统验证与调试

在完成 DDR3 接口电路设计之后需进行系统验证和调试。Vivado 调试功能可对数据传输全程进行监测,从而有效解决潜在问题。此外,Logic Analyzer 等外置工具也能助力系统深度剖析。

需悉心监控系统验证过程中的数据传输准确性与稳定性,并依据实际状况微调参数,以此提升系统效能。严谨的验证与调试过程可确保DDR3接口电路设计符合预期期望,进而满足现实使用要求。