1. DDR3内存条简介

DDR3内存条,作为常見的计算机构件,主要负责储存数据与指令。此款双边输入输出(Double Data Rate)内存,相比前代DDR2内存,在传输速度及节能方面有显著进步。DDR3内存条是众多晶片元素构成,每枚晶片包含复杂的电路结构,决定其性能的重要因素包括电路链接以及操控。

在DDR3内存条中,电路的职能事关重大,即连通各部件、输送数据以及调控信号。精妙的设计与布局使得DDR3内存条具备稳定而高效的数据读取写入功能,从而提升了计算机系统的性能表现。

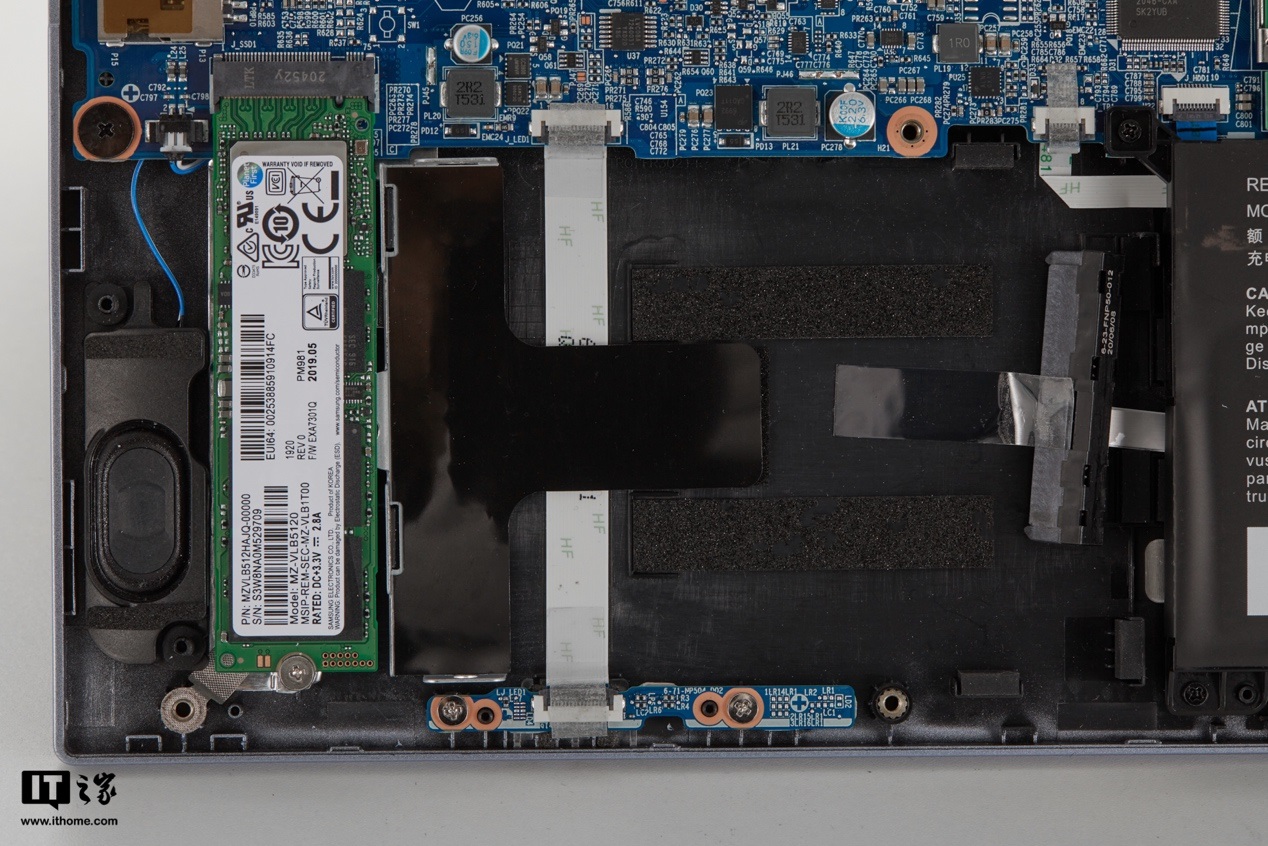

2. DDR3内存条电路结构

DDR3内存条的电路结构较为复杂,由多种线路构成,如数据线、地址线以及控制线与时钟线等。各线路精密排布以保证信号稳定可靠地传输。

在DDR3内存模块的设计中,数据导线担负着有效数据的传递使命,地址线则用来指引数据的读取与写入区域,控制线则以此来调节最优的数据传输路径。而时钟线的存在,让所有器件能够有序协同工作,从而保证了数据传输的精准度以及一致性。

3. DDR3内存条电路设计原理

DDR3内存条设计需兼顾信号传输、时序掌控及能耗管理等多重因素。关于信号传输层面,需特别关注信号干扰与延迟问题,采用差分信号传输提升抗干扰能力;在时序控制环节,致力于保证各信号传输的准确性和及时性;至于能耗管理,需要在不影响性能条件下,寻求降耗策略。

DDR3内存条在设计过程中需全面考量这些要素,经过精密调整与优化,从而达成高效能、低能耗之目标。

4. DDR3内存条电路中的关键技术

在DDR3内存条电路设计中,采用了多种尖端科技来确保其具备高性能表现。其中包括自校准技术(ZQ Calibration)、预取技术(Prefetch)和错误校正编码(ECC)等等。这些先进技术不仅能够提升内存存取效率,还能实现更加稳健的数据传输,同时进一步增强了设备整体运行稳定性。

自校准技术有助于DDR3内存适时调节环境反应参数,提升稳固性与可靠性;预取技术透过前置载入数据以降低访问延时,强化读写效能;纠错码则可发现并修正在数据传输阶段所产生的误差。

5. DDR3内存条电路与计算机系统性能

在计算机系统中,DDR3内存在其中扮演关键角色,是整体性能与稳定运行的关键因素。优化的DDR3内存电路设计能带来更快且更加可靠的数据访问体验,加速应用启动并提高操作反应速度。

优质的DDR3内存条配置与巧妙电路设计相结合能显著提升计算设备的总体性能。特别是大负荷应用运行及多项任务同时执行时这一设计理念变得至关重要。

6. DDR3内存条电路发展趋势

伴随着科技的持续进步与市场需求的剧烈变动,DDR3内存条电路的演化过程始终在持续进行。毫无疑问,未来的主要方向将集中于提高工作速率,降低能耗以及扩大存储容量等方面。此外,智能化和自适应性领域同样可能带来更多的革新成果。

在不久的将来,DDR3内存条将具备更强大的节能环保与智能管理能力。在此基础上,这样既能保证其高效性能,又提升使用体验且兼顾环保因素。

7.总结与展望

在细致研究DDR3 内存条电路结构、设计原理及关键技术的基础上,结合其在计算机系统性能表现的影响力,我们可以全面了解并深度体会该核心部件在整个领域所产生的重大影响。预计在未来科技持续飞跃和创新拓展的背景下,DDR3 内存条电路将显现出更为丰富多元的发展潜力。