什么是Hyperlynx DDR仿真

在当今日新月异的高速电子产品设计中,双倍数据速率(DDR)内存已主导市场潮流。Hyperlynx公司研发的DDR仿真工具则成为设计工程师不可或缺的利器。这一仿真平台通过模拟信号完整性与时序分析,助其轻松评估并提升DDR接口性能,使得整个系统保持稳定运转。Hyperlynx DDR仿真系统不仅具备覆盖全面的功能如布线、时序分析及信号完整性分析等,还为复杂设计过程提供有力支撑。

在DDR接口设计领域,设计工程师需重视信号传输延迟、时序关系以及布线走线等环节,而借助Hyperlynx DDR仿真技术能有效协助他们在设计过程中及时发现问题并提出相应对策,从而实现节省时间及降低成本,提升设计品质之目标。

为什么需要进行Hyperlynx DDR仿真

DDR接口设计可能面临诸多挑战,例如:信号完整性的弱化会引导时间顺序偏差;无规划布线会引发串扰。在硬件检验阶段方知这类问题无疑将拖长产品研发周期,提高成本。然而,借助于Hyperlynx DDR仿真技术,我们能在设计环节便对接口性能进行全面考量,以便在设计方案出现滞后时迅速纠正。

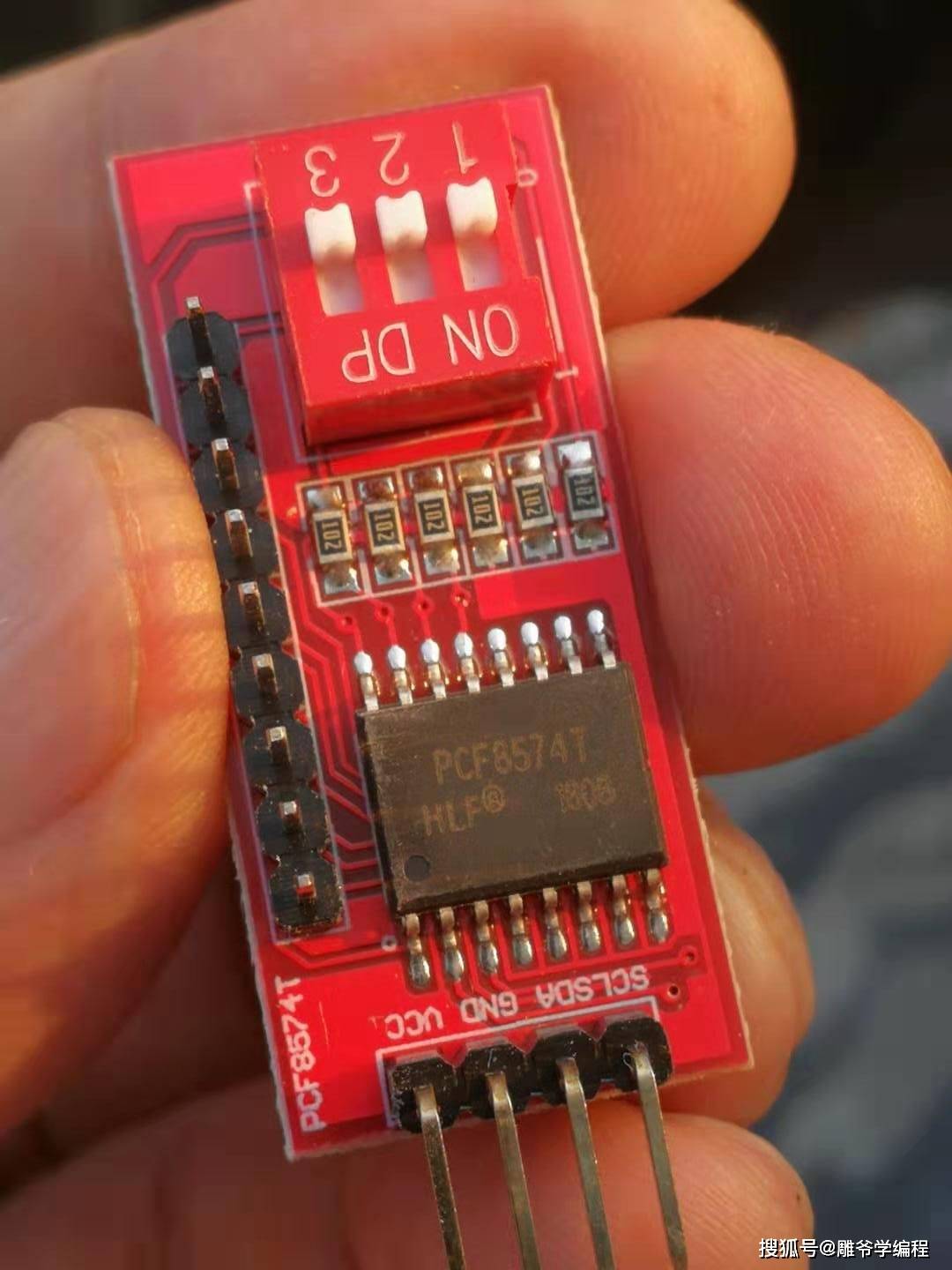

尤其是对于高速数字系统,其信号的完整性直接决定了整体性能,而借助于Hyperlynx DDR仿真软件,可精准模拟信号在电路板各层以及布线过程中的传输情况,协助工程师进行信号质量分析与改善,从而降低串扰及反射等不良问题对系统效能的不利影响。

Hyperlynx DDR仿真的应用场景

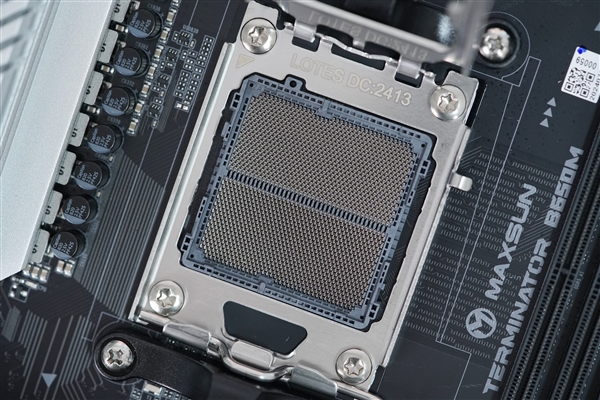

Hyperlynx DDR模拟技术被广泛运用于各类高阶数位系统(如电脑、通讯硬件、消费类电子仪器等)的设计过程中。而以DDR内存为核心的存储组件在此之中发挥着举足轻重的作用,对于整体系统效能与平稳性的影响不可忽视。因此,这些系统的设计阶段必定会进行与DDR接口相关的模拟验证。

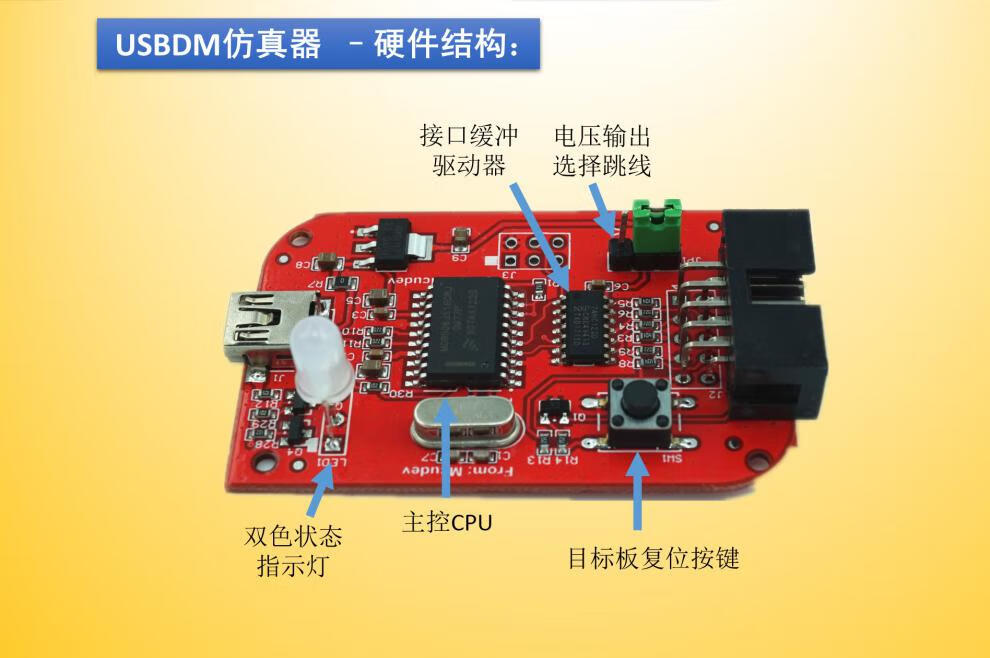

嵌入式系统的DDR接口通过稳定性控制因其小体积和低能耗特征而更显重要。借助Hyperlynx DDR仿真的优势,能够让工程师迅速检验DDR接口设计并优化其效率,进而保证系统的稳定运作。

如何进行Hyperlynx DDR仿真

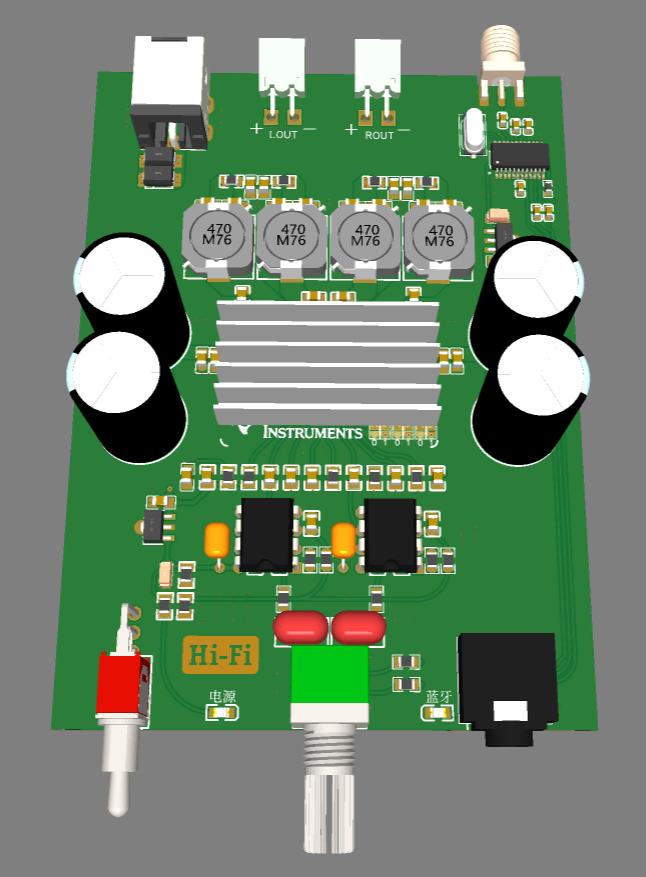

进行Hyperlynx DDR仿真的流程主要包含五个环节:构造模型、设定信号源、配置仿真参数、执行仿真以及解析结果。首先要依据实际硬件构成精确的模拟模型,并对输入输出信号源加以明确界定。随后,需调整例如时钟频次、数据传输速度等仿真参数,启动仿真过程后即可获知相应的波形图表及报告数据。

借助对波形图及报告数据的深度剖析,工程师可准确把握信号传输速率与时间顺序的合理程度,进而制定对应优化策略。同时,在Hyperlynx DDR仿真软件的支持下,专家们能够以直观易懂的方式掌握系统表现,据此做出更为精确的决策。

未来发展趋势与挑战

面对日益增加的电子设备复杂性以及多样化发展趋势,DDR接口设计面临巨大挑战与压力。未来,随着诸如5G及人工智能等先进技术的日渐普及,对于DDR内存接口的需求将更为紧迫。为了应对这一形势,Hyperlynx DDR仿真技术必将持续创新,满足新时期的市场需求。

然而,未来潜在的困难包括高速数字系统中信号完整性的复杂化及其布局布线的瓶颈。因此,我们需继续完善 Hyperlynx DDR 仿真工具的性能,并结合实践案例来应对这些挑战。