什么是DDR ZQ校准

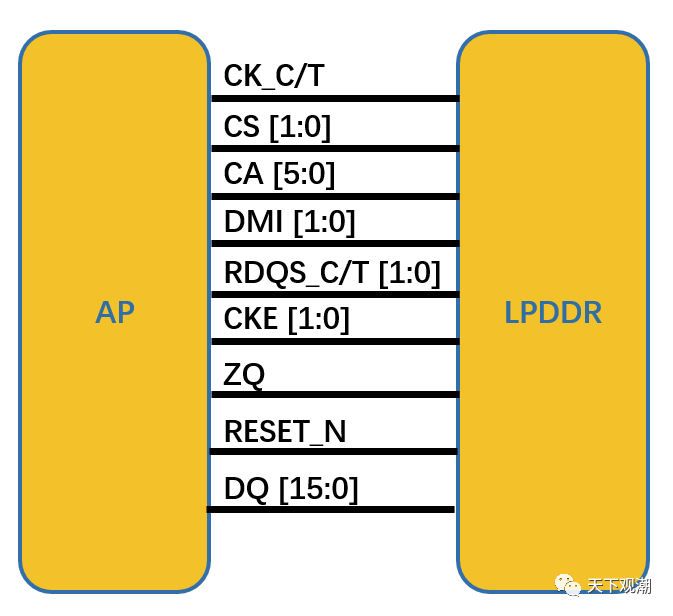

DDR ZQ 校准,即依据规格参数变动实施的内存精确调试策略,服务于DDR存储设备和DRAM芯片间的交互。其旨在优化DRAM内部阻抗,保障数据传输的持续性及稳健性。经过该步骤的处理,能够显著增强内存效能并减少数据交换过程中的错误发生率,进而全面提升系统运行效率。

在DDR SDRAM中,ZQ校准对于保证内存子系性能稳定具有关键意义。若内存控制芯片与其DRAM芯片间有阻抗差异,就可能引发时序偏差及信号失真的情况,这对系统运行产生不利影响。故,精准调节ZQ数值可有效减轻上述问题。

DDR ZQ校准的原理

DDR ZQ校准基于内存模块内的终端电阻,此电阻旨在匹配传输导线的阻抗,以保证信号传输的完整与稳固性。ZQ数值反应了终端电阻的大小,在DDR控制器初始设定阶段,应根据具体情况选择适当值,以适应不同的系统环境及运行状况。

在系统启动或温度变化之际,内存控制器定期对ZQ值实施精确调节。通过向DRAM芯片发出精确指令,该控制器能实时获取ZQ值并进行精细调整,直至达到环境条件下的最优性能。这种高效的自动校准机制,不仅能够精准抵御外部环境干扰,也使得内存子系统始终保持在最高效运行区间。

DDR ZQ校准的实践意义

DDR ZQ校正在实践应用中的重要性不容忽视。例如,在大数据处理、图像渲染等高速数据传输环境中,内存子系统的稳定直接影响整体系统效能。通过精细化调整并校正相应的ZQ数值,有助于降低因误码率及时序偏移等因素引发的数据传输风险,从而提升成功速率与效率。

其次,在多通道内存系统架构中,各通道之间易出现信号干扰及时序不统一现象。而对每通道进行独立的ZQ校正调整,能彻底根除这些不良因素引发的通道之间失配现象,大大提升系统整体运行稳定度与可靠性。这项精准的调节策略,有力地将多通道内存系统架构在繁重负载环境中的最佳效能展现无遗。

此外,在超频或过度负载的条件下,DDR ZQ校准的重要性尤为凸显。根据具体情境实时调整ZQ参数,可让内存子系统更好地应对高频、重载环境,并避免数据传递中的遗失与误码等状况。此智能调控策略有助提高系统超频性能及稳态运作效果。

结语

DDR ZQ 校准作为关键内存控制技术,具有提升系统稳定性、可靠性及性能之功效。其通过精确调整 ZQ 参数,消除内存子系统中的阻抗不匹配现象,实现数据传输过程中的信号完整性及稳定度。未来硬件设计优化过程中,需高度重视 DDR ZQ 校准技术,持续改进实施策略,实现在满足日益增长的计算需求方面取得更大突破。