DDR内存简介

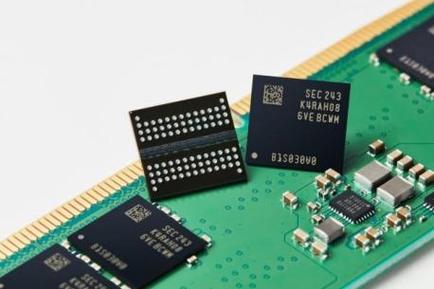

DD(Double Data Rate)内存作为高效能的计算机存储器之一,其高速与低能耗使其在各电子设备领域得到广泛运用。借助提升数据传输速率及频率,DD内存能在单次时钟周期内完成两次数据传输,大大提升数据传输成效。在DD内存运作过程中,DQS(Data Strobe)信号发挥着举足轻重的角色,作为数据传输有效性的指示器,在同步与校准方面发挥关键作用。

DQS信号,即是DDR内存中的特异讯号之一,此信号以数据信号同步传送,时刻与数据紧密关联,以期确保证据的准确读出及写入。读取阶段,DQS信号带动采样时机;写入阶段,则及时稳定输出数据。可以说,DQS信号的稳健性与精准度,决定着DDR内存系统的良性运转。

DQS信号的作用

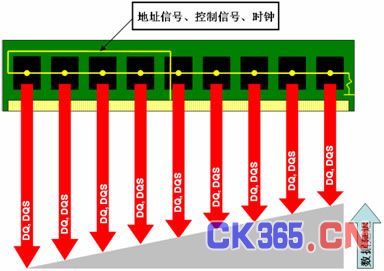

数据采样策略:当我们访问存储器中的数据时,DQS信号会根据DQ(Data)信号设定相应的数据采样时刻。这样做可以确保我们在恰当的时间点获取所需的准确数据信息。

数据放大操作:在数据写入过程中,通过控制 DQS信号来促使内存controller维持数据稳定性,从而保证读出数据的准确性以及抗干扰能力。

时序配置:利用DQS信号进行时序校正,调整其与时钟信号间的极性关系可达致数据传输时间顺序的精确度。此举对DDR内存系统运作效率具有显著提升。

DQS与时钟(CLK)信号

在内存系统中,除DQS信号外,时钟(CLK)亦是关键要素。CLK驱动内存运行频率,且DQS与CLK需保持一定时序对应,以确保通道顺畅。通常,DQS相较于CLK提早或拖后一段固定延时,此即为延迟。通过微调延迟值,可使DQS与CLK达到精密配合。

DQS延迟量调整

为确保DDR内存系统正常运行并实现最优性能表现,需对DQS延迟量进行精细控制。在大部分情况中,DDR内存控制器可自主完成DQS延迟量的培训与调整,此工作在初始化阶段已经全面开展。然而,特殊情况下用户仍有机会自行调节DQS延迟量,追求系统性能的进一步优化。

调节DQS延迟需使用专用设备或软件进行微调,操作时务必慎重,以免产生次生危害。可采用增减法调整延迟量,经多次测试后找出理想的设定值,从而提高系统稳定性及响应效率。

DQS训练技术

近年涌现出的多项新型技术与方法帮助我们简化并提升了DDR内存系统对于DQS延迟量的训练与调整流程。其中之一在于采用人工智能算法的自动化训练方案,该方案能够在系统启动阶段自行学习与适应用户需求以动态确定最理想的DQS延迟设定值。

自动训练技术可显著简化DDR内存系统的配置及优化流程,同时提升其稳健性与性能。通过持续学习并适应系统环境变迁,该技术能进行智能化调节,以期将DDR内存系统调至最优水平。

结语

综合而言,对 DDR 内存中的 DQS 信号进行深入理解具有举足轻重之地位,其中涵盖了诸多技术难题,如数据传输各环节的协同配合以及时序校准及延迟量度调节等方面。全面通晓与精准把握关于 DQS 信号的相关知识,对 DDR 内存系统的设计、优化及维护起着决定性作用。

期望此篇文章能协助读者深化对DDR中DQS的了解,并在实践运用中考量其要点。如有不解或建议,敬请随时提出共同探讨!