DDR走线的重要性

以DDR为核心的现代电子设备设计,使得走线质量对其整体性能产生了直接影响。因此,DDR走线设计的重要性不言自明。优良有效的DDR走线设计能提升信号的完整性,降低串扰,从而保障系统的稳定运行及卓越性能表现。然而,进行此类设计需兼顾信号完整性、匹配长度、层次规制等多重目标。

在DDR走线设计领域,信号完整性的重要性不言而喻。它涵盖了信号的时序、电压波形及噪声容忍度等多元化范畴。值得注意的是,在DDR传输过程中,时序问题极为关键,微小的时间延迟差异便可能引发数据传输误码。因此,在布局DDR走线时,务必确保信号沿途的时延保持高度一致,以防止性能波动和时序违规现象。

此外,DDR走线设计中,匹配长度是至关重要的考量因素。这源于DDR采用了双边沿采样机制,使数据传输必须遵从各数据线尽量等长的原则,否则易产生时序误差。常见做法包括采用匹配linelength技术或采用飞线的方式,确保每条数据得以在同一时刻抵达目的位置。

层叠规则与差分对

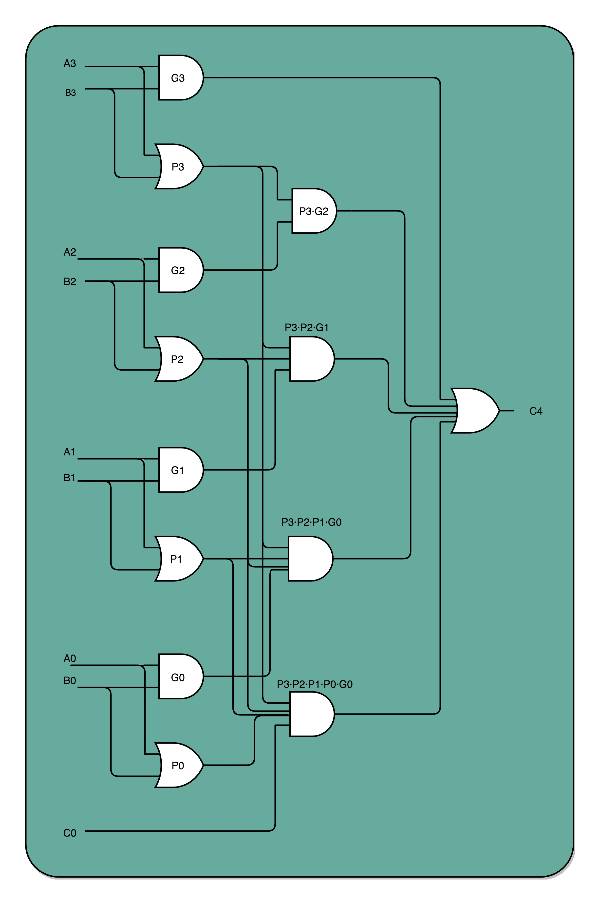

在DDR布线规划中,层叠规范乃至为关键之要素。通过准确设定PCB板材厚度与介电常数这类参数,便能增强差分同路间的隔离,减轻串扰所造成的困扰。妥善的层叠规制可显著提升信号完整度及抗干扰性能。

差分对乃DDR传输之主要信号传输模式;设计DDR布线之时,尤为关注其布局以及走线规则。简单而言,差分对由正负两信号线各自呈镜像排列构成,力求使信号线间间距等距且远离其他信号线,以降低串扰影响。

终端电阻与阻抗匹配

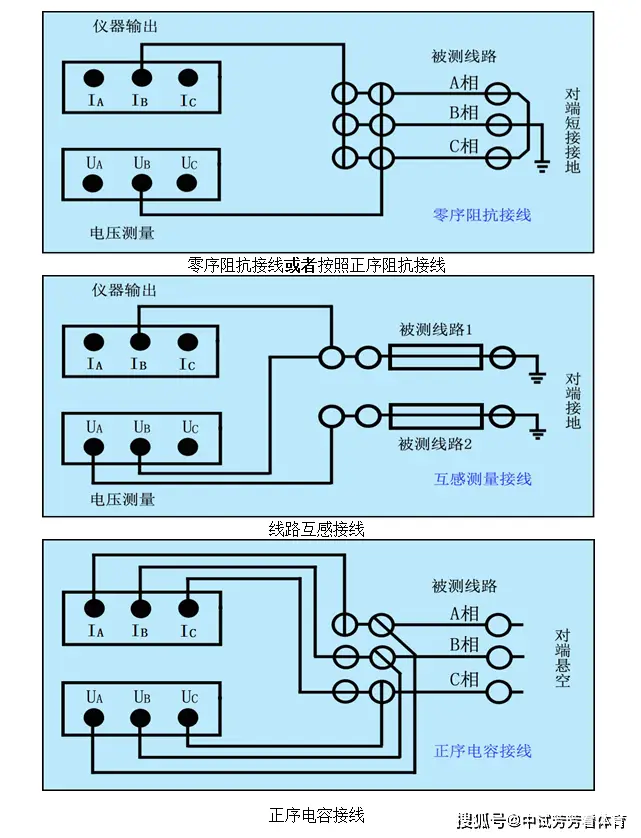

DDR走线设计需重点关注终端电阻与阻抗匹配问题。终端电阻用以降低反射波,保证信号质素,其数值常依据PCB板电气特性而定。实施过程应结合PCB材质与布线细则,定制最适阻值,并将其有效接入差分对两端。

在DDR布线规划时要重视阻抗契合度。鉴于其数据传输对阻抗契合性的严格要求,需在布局与路线设计阶段保持差分解结构朗诵环境阻抗恒定并维持低至小的改变。

布局原则与参考平面

优秀的布局原则,是保障DDR系统正常运行并确保其稳定性之基石。无线缆设计应奉行短且直、广且平、致且整之原则,避短以及过窄之路径;预留充足空间以满足终端电阻及滤波器等组件需求,杜绝数字与模似信号混入产生干扰。

参考平面设定对 DDR 系统性能起着举足轻重的作用。适当调整参考平面配置能够显著降低信号回流路径阻力,增强系统整体稳定度及抗扰性。参考平面设定过程中务必确保其与信号层间留有充足空间以减小相互干扰。

仿真验证与调试优化

最终,在完成双倍速率动态随机存储器(DDR)布线设计之后,仍需实施仿真检验以及调试优化措施。借助仿真工具模拟数据传输过程,有助于早期识别潜在问题,并及时调整及优化设计方案;在此基础上,在实物硬件调试阶段,应运用如示波器与逻辑分析仪等仪器观测信号波形,进一步提升系统性能。