什么是DDR上拉电阻

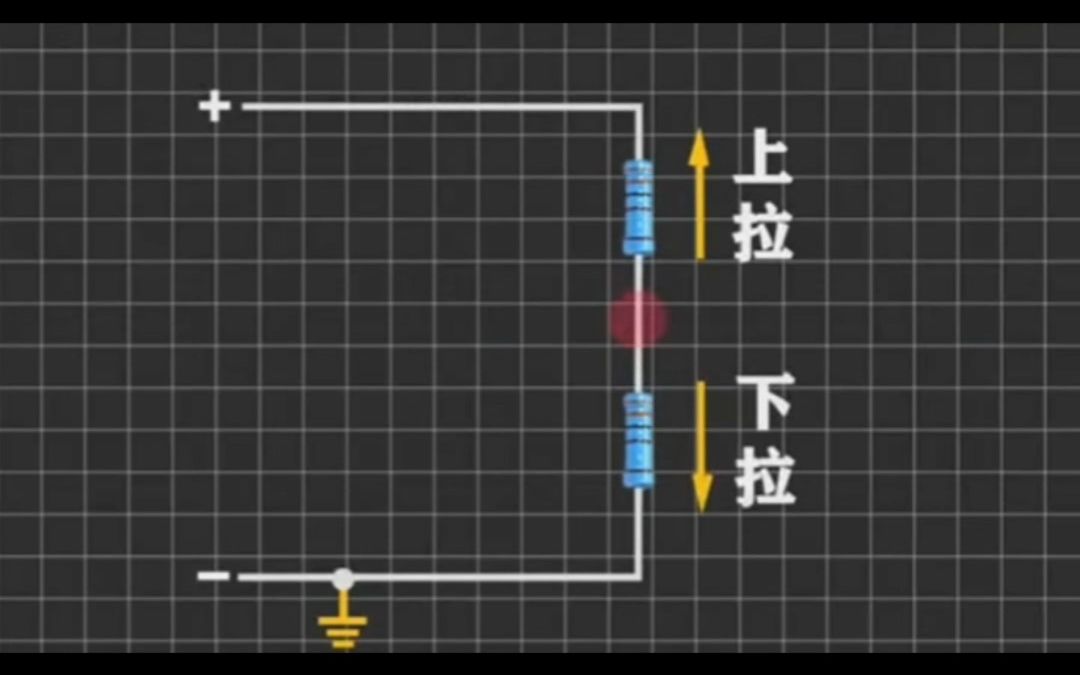

在数字电路设计领域,双倍速率(DDR, Double Data Rate)存储器是一种典型,其内部包含了上拉电阻这样的关键器件。可以理解为,上拉电阻实质就是将信号线路连接至高电平状态的元器件,旨在维持信号线在无操作情况下的高电平状态。尤其在DDR的运作过程中,上拉电阻发挥着举足轻重的作用,保证了数据传送的精度与稳定性。

在上拉电阻的设计中,其主要功能在于将数据线或地址线与电源相连,在DDR设备中的主要作用是维持信号线稳定,降低噪声干扰并提升抗干扰性,进而提升系统整体表现和稳定性。而具体操作过程中,通过精确设置电阻值及连入方式便能显著提升DDR系统的运行效率和可靠性。

DDR上拉电阻的作用

在DDR中,上拉电阻主要起到以下几个作用:

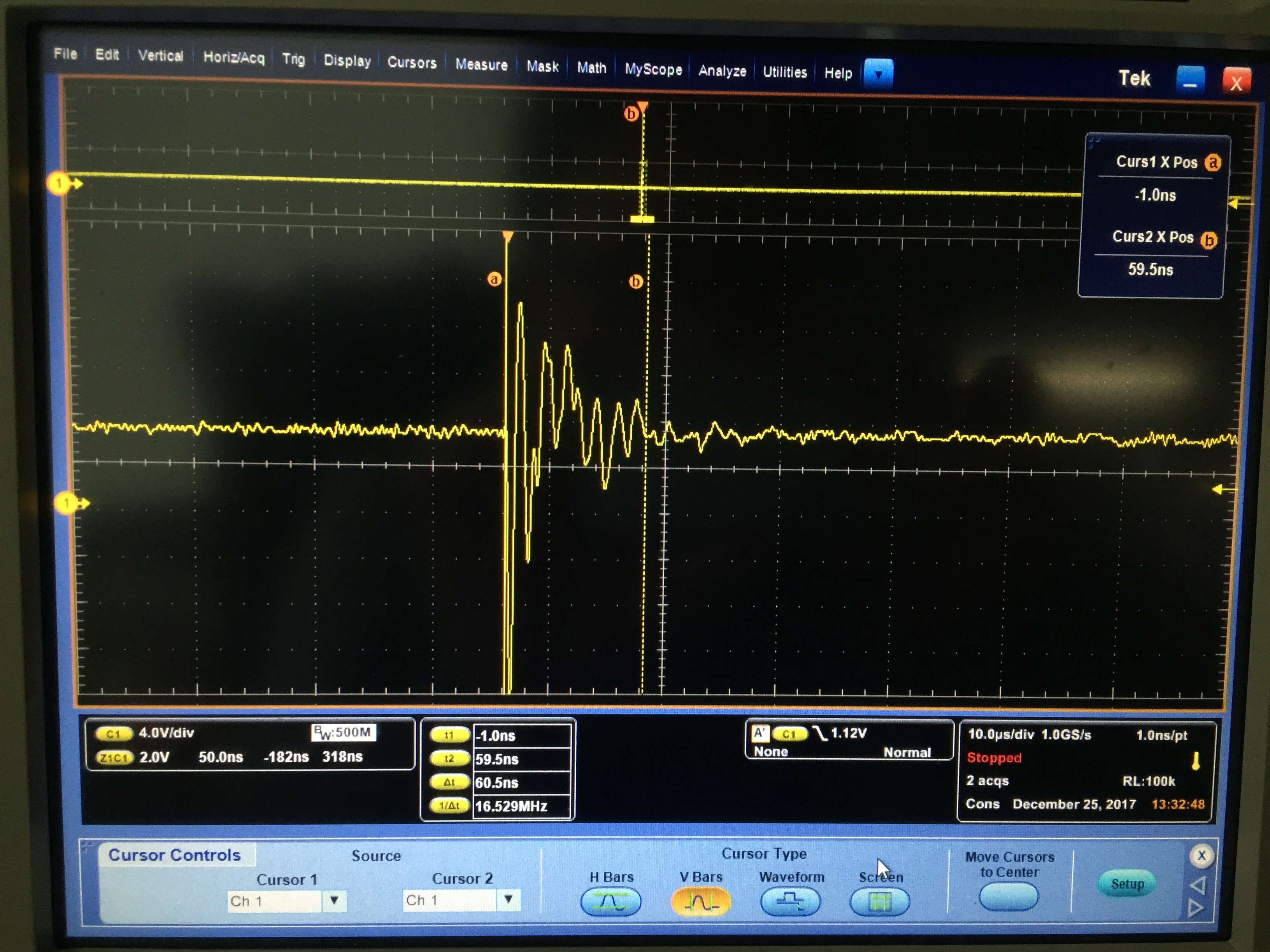

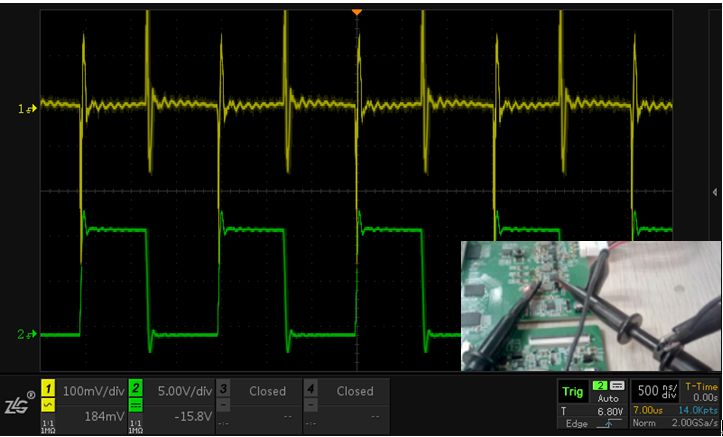

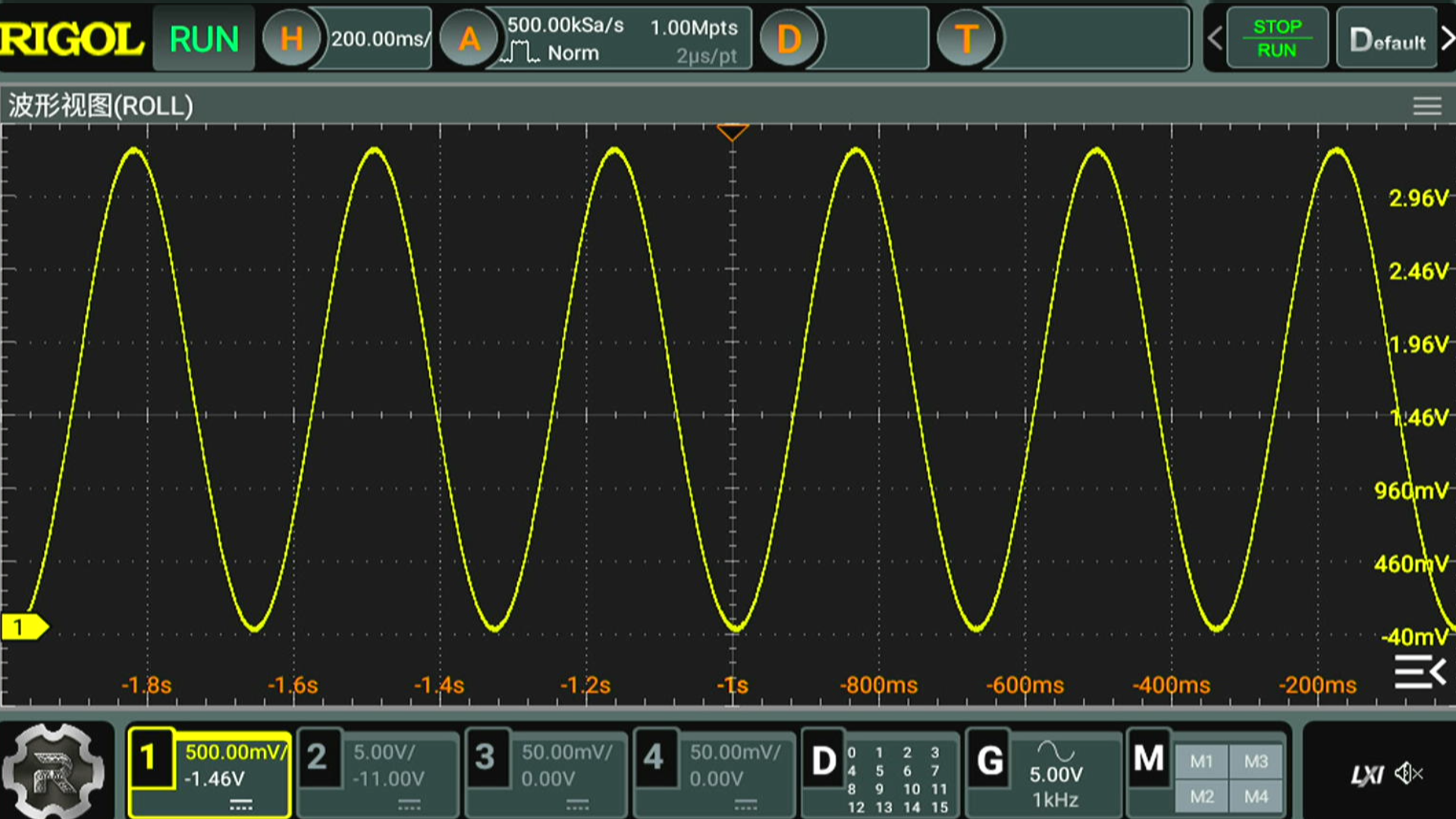

维持信号线稳定:在无任务期间,利用上拉电阻使信号线上移至逻辑高位,以防止信号随机波动产生错误判断。

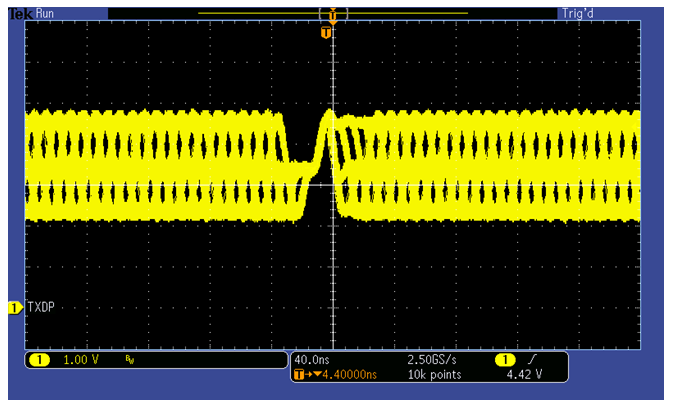

控制信号传输:在上位机和下位机间的数据传输期间,可利用把握上拉电阻状态来调控信号速度及稳定性。

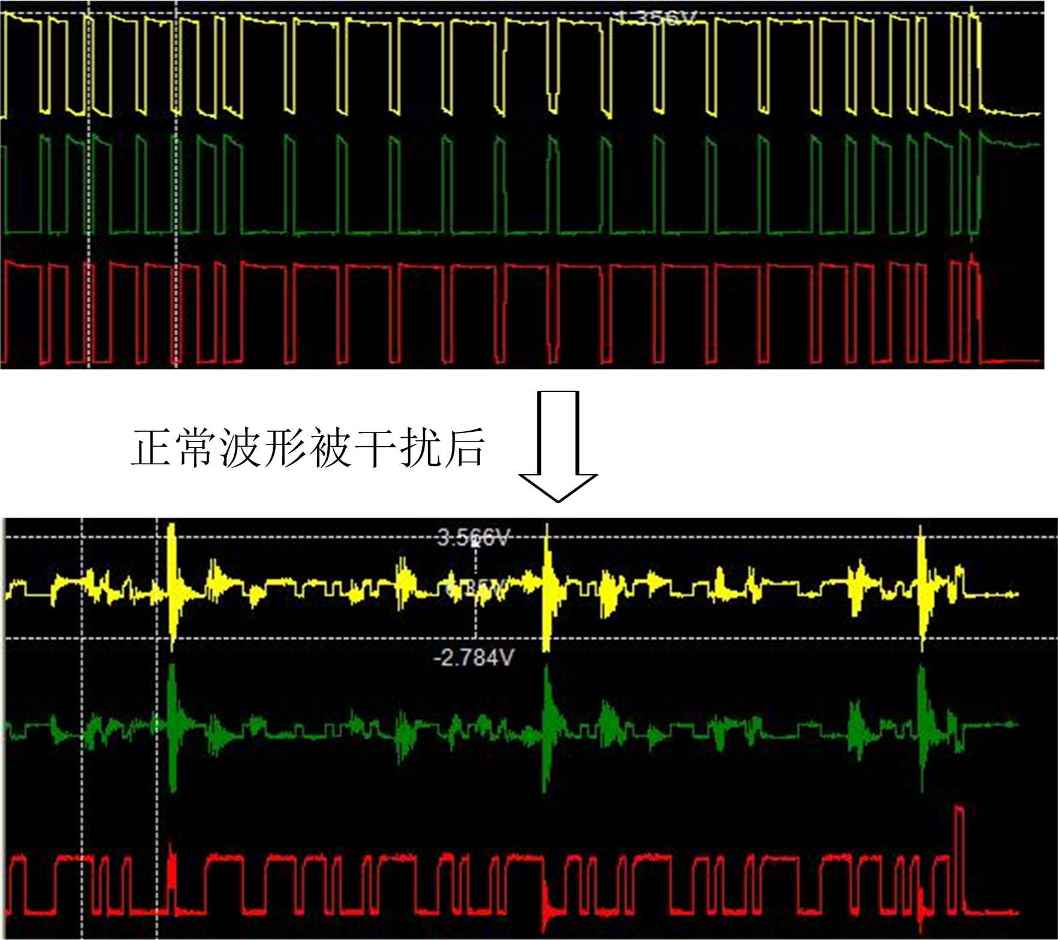

改善抗干扰能力:恰当运用上拉电阻可有效增强系统的抵抗外场干扰的能力,降低信号传输受干扰的风险。

降耗提效:优化上拉电阻设计可降低功耗,提高整体系统性能。

如何选择合适的DDR上拉电阻

选择适宜的DDR上拉电阻对提升系统性能至关重要,主要考虑以下几个关键性因数:

依照系统需求与传输特性选取适宜之阻值,大致介于数十至上百欧姆区间。

误差容忍度考量:面对生产实现中的误差以及环境变化可能带来的影响,需选用能承受较低误差的上拉电阻。

环境温度影响:深入研究上拉电阻在各种温度条件下的功能稳定性,细选满足设备工作环境温度要求且性能稳定的品种。

抗扰度:优选具有卓越抗干扰性能的上拉电阻,保证数据传输稳定无误。

DDR上拉电阻布局设计注意事项

在DDR系统架构设计过程中,优秀的电路布局与配置能有效提高设备整体运行效能及稳定性。关于DDR存储器的上拉电阻布局安排,须遵循以下原则:

使电阻贴近接口:尽力缩短信号线长度以降低传输延迟与损耗。

抗干扰性:应防止多条信号线共用同一个上拉电阻,以避免产生干扰导致数据传输失真。

布局优化:精确设立地线的布置方式,保障地线与信号线间的安全间距,缩小地回路对信号干扰的可能性。

差动信号处理:精确区分差动信号,并充分利用正确的差动对策略配置上下拉电阻。

如何优化DDR上拉电阻设计

优化DDR上拉电阻的设计有助于提高系统性能与稳定性,以下是几项可行方案:

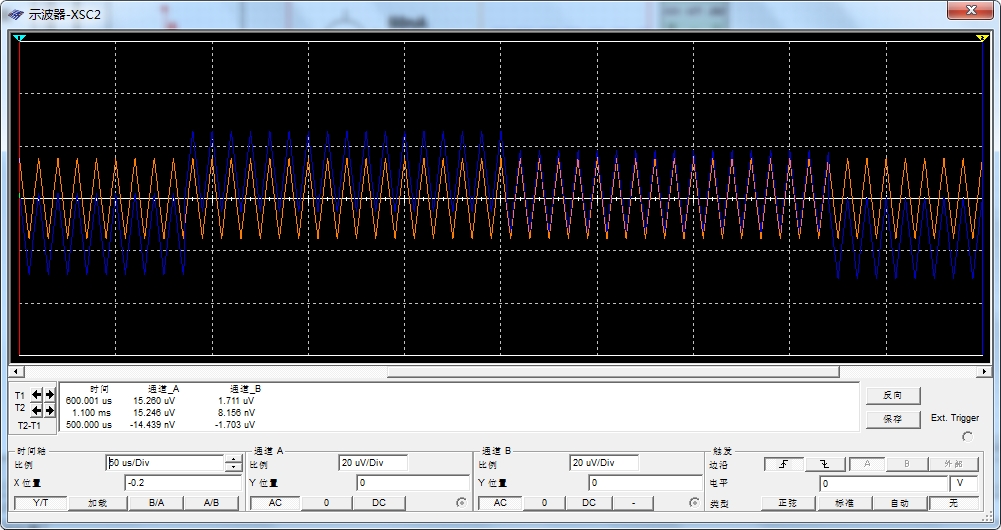

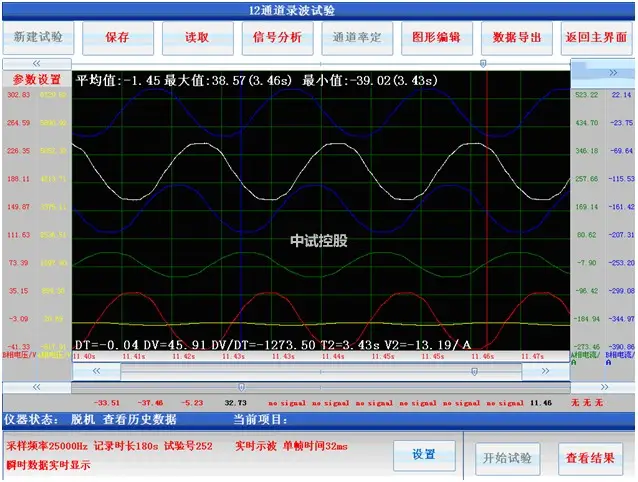

模拟验证:运用仿真技术对各参量条件进行模拟实验,依据实验成果调整参数至最优水平。

实践测试:通过实践的测试环节,验证优化后的方案是否满足设定的期望要求,进而依据测试结论做出相应的反馈和调整。

升级完善:时刻关注科技革新的步伐及行业动向的改变,对DDR拉电阻进行精确完善,满足现代需求。

结语

DDR 上拉电阻作为数码系统中的重要元素,对于确保数据的精准和稳定传输具有至关重要的作用。深入研究其运作原理、选配技巧、布线设计要领及优化对策,有助于我们更好地运用到实际工程领域中,同时提高整个系统性能。