伴随着科技进步,作为计算机常用存储设备的DDR3内存的时序分析变得至关重要。本篇文章深入研究了DDR3时序理论、参数设置、分析工具及验证策略等相关议题,意在助力广大读者更加全面且精准地理解并运用DDR3内存技术。

一、DDR3时序概念

DDR3内存(又名双倍速率同步动态随机存取存储器),是采用同步动态随机访问技术的存储设备。它具有在一个时钟周期传输两次数据的能力,使其拥有较高的运行速度与带宽。DDR3的时序则是描述资料传输中的时间与信号控制等关键参数。

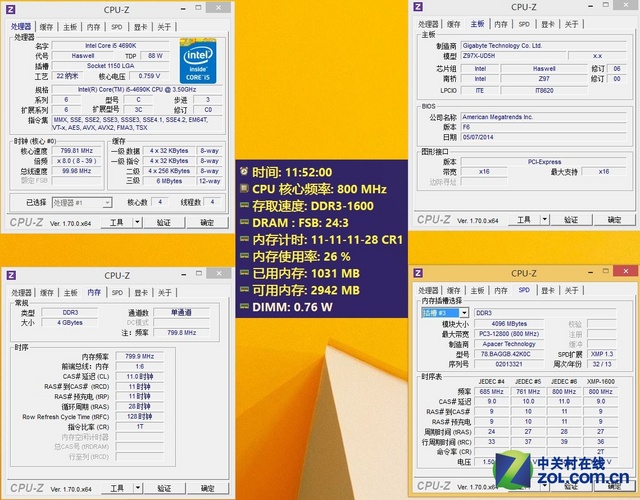

DDR3内存的时序控制主要涵盖预充能时间(tRP)、行地址脉冲延迟(tRCD)、列地址脉冲延迟(tCL)以及写入保持长度(tWR)这几个元素。这些时序特性对其工作效能与稳定性具有关键性影响,故精确掌握并适时调整这些参数至关重要。

二、时序参数

预充时长(tRP):此为读写动作间用以预先充能所需的周期性时段,通常由内存模块自身属性与主板设计决定。

行动地址选通时长(TRCD):为发出行动地址信号至本行可访问数据输出间所需延迟。

行地址预充时长(TRP):即上一行关闭至下一行开启之间必须等待的延迟时间。

tCL(列地址选通时间):指从发出列地址信号至相应数据可用输出之间所需的延迟时长。

保存在磁道上的时间(tWR):即指完成写操作后,保证有效数据维持需达到的最短时间。

这只是DDR3内存的其中几个关键时序参数,灵活应用它们能提升内存读取与写入效率及整个系统性能。

三、时序分析工具

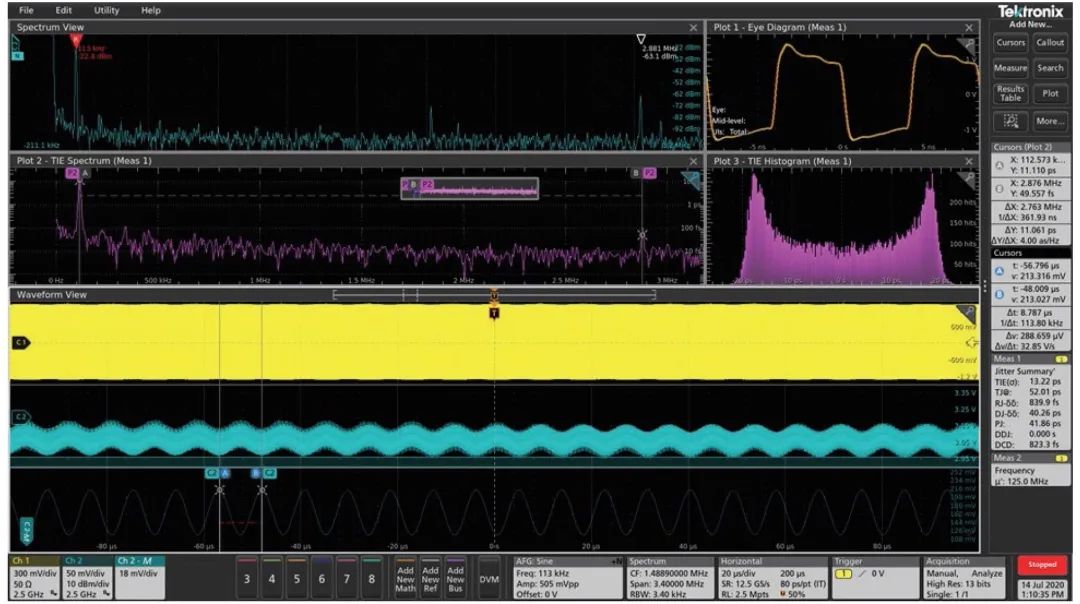

在深度动态随机存储器(DDR3)时序分析领域,运用先进的专业工具能有效提升工作效率及精确度。诸如SignalTap规律分析器与ModelSim之类的软件工具都被广泛使用,这些工具能够捕捉并精准分析DDR3内存控制信号以及数据信号的情况。

SignalTap逻辑分析仪是一种以FPGA为基础进行实时信号监控与图形展示的工具,能协助工程师迅速识别潜在问题。而ModelSim软件,作为常用的数字电路模拟及测试验证软件,通过有效的仿真校验,能深入理解DDR3内存运作时各信号间交互情况。

四、时序验证方法

仿真验证:运用ModelSim等模拟测试软件,对设计完成的DDR3控制逻辑模型实施仿真确认,检测各信号是否与预设相符。

逻辑剖析:运用诸如SignalTap Logic Analyzer等工具对DDR3的控制信号进行实时捕捉检查,确保其波形吻合规范要求。

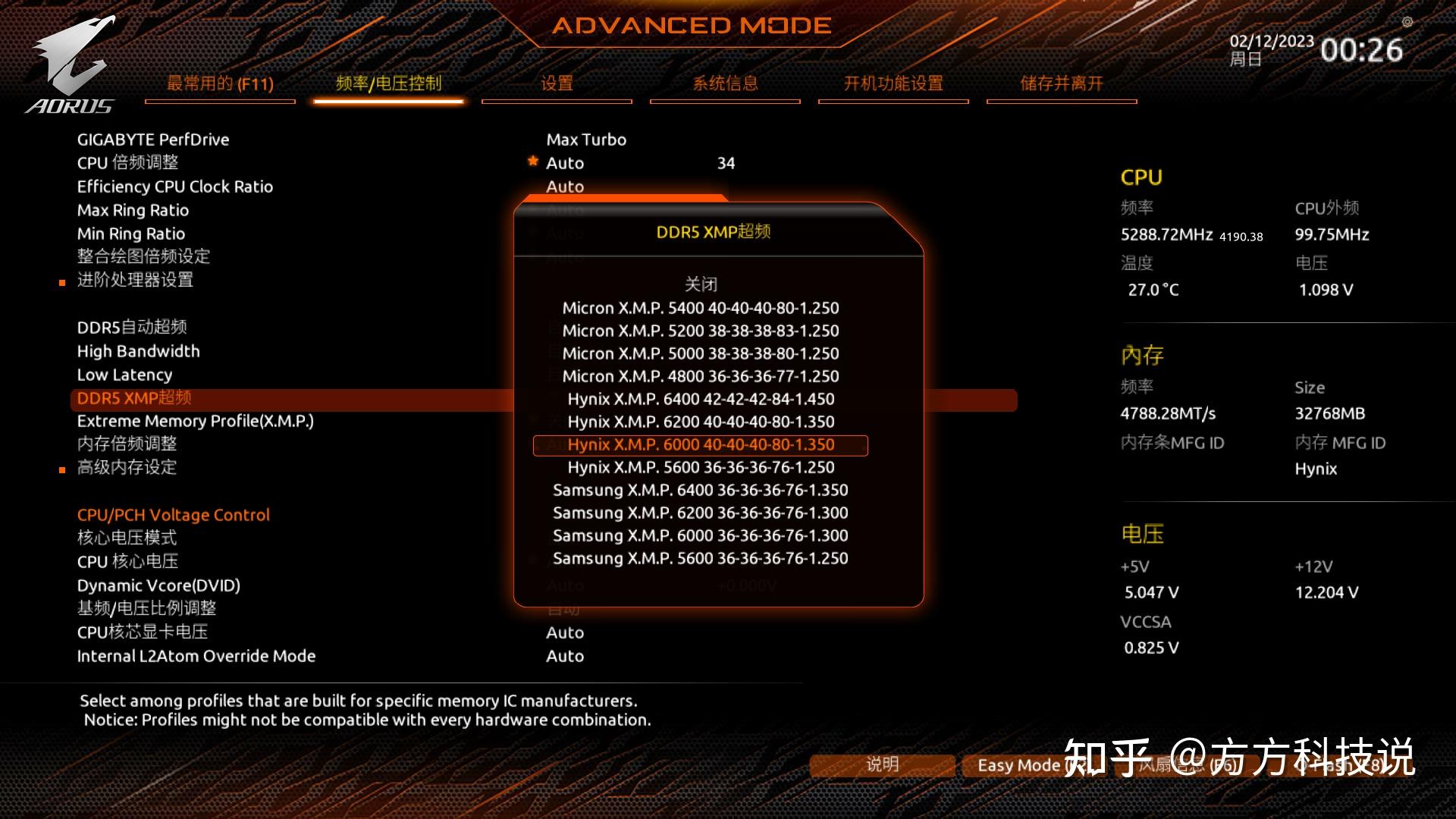

时序校验:通过对主要时序参数的精细调整和实际测试数据的比照验算,以求得最佳配置策略。

采取这些策略可全面而深入地核实DDR3内存时序设定的合理性,即时发现及解决可能存在的问题,确保系统稳定且性能良好。

五、应用场景与优化建议

实践运用:DDR3内存在电脑、服务机以及网络设备等领域均有广泛运用,尤其针对大量数据处理及高速计算需求的实际情况表现尤为显著。

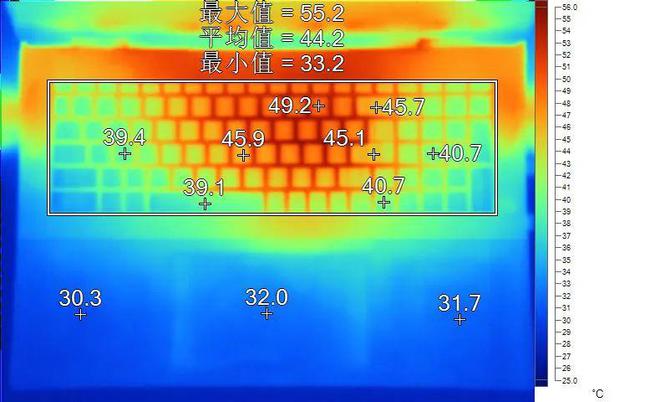

改进方案:依据实际情况对DDR3内存参数做出恰当设定,并参考实际实验数据进行优化调整。同时注重维护适宜的散热条件,避免高温对内存性能产生不良影响。

六、未来发展趋势

科技的飞速发展与市场需求的持续变革,使得诸如DDR4、LPDDR4这类新一代存储器标准逐步走进人们视野,得到了广泛应用。展望未来,我们可以预见更多兼具高性能和低功耗的创新成果将会涌现,同时也将伴随着更加专业化的设计方案,这些设计无疑将更好地服务于大数据处理及人工智能等关键领域。

七、总结与展望

本文对DDR3时序分析进行深度剖析后,望读者对DDR3内存的本质及重要性有所洞察。在未来的成长道路上,鼓励您广泛实践探索并分析挖掘相关文献,充分利用宝贵的经验和知识,提升自身硬件设计水平与创新能力。

敬请阅读者留下宝贵意见,分享您对于DDR3时序分析的认知。展望未来,新一代内存标准化又将如何演变呢?我们期待着与你的探讨和交流。