什么是DDR SDRAM控制器

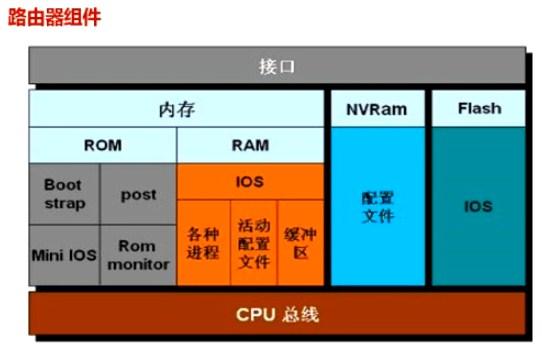

探讨DDR SDRAM控制器前,应先理解其基础含义。DDR SDRAM,即Double Data Rate Synchronous Dynamic Random Access Memory,为双倍数据传输速率同步动态随机存取存储器之简称,兼具高带宽与同步定时特点。而其控制器,即DDR SDRAM控制器,肩负起对DDR SDRAM存储设备的监管和调控职能,连接处理器及存储器间数据传输及通讯,发挥桥梁作用。此类控制器设计优越与否,直接关联到系统稳定性、运行速度以及能耗等关键因素。

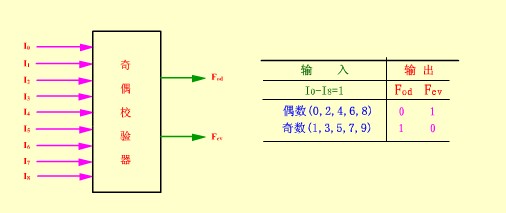

在技术层面上,DDR SDRAM控制器涵盖了诸多功能模块,如时序控制、地址产生、指令发出、数据缓存以及错误检测及纠正等。这些模块共同作用,促使DDR SDRAM控制器实现高效的数据存取,同时确保数据精确度和稳定性。

DDR SDRAM控制器的工作原理

DDR SDRAM处理器在整个系统运作过程中承担了关键的角色。它的运行机制可以归纳为如下几个主要环节:

时序严谨:DDR SDRAM控制器须依照预定的时序标准,精准地产生所需的时钟信号,从而保证数据在准确的时刻进行传输。

地址映射:依据处理器传送来的地址信号,DDR SDRAM控制核心需研制出相应的行和列地址,以便定位待读/写数据的位置。

指令执行:根据处理器传来的读写请求,DDR SDRAM控制器将发出相应的存取指令至存储模块。

数据缓存:DDR SDRAM控制器需运用缓冲机制保障数据传输流畅稳定。

误码检测及修正:DDR SDRAM控制器须具备数据传输错误检测及纠错功能,确保精确的数据传输效果。

透过对上述操作机制的解析,我们发现DDR SDRAM控制器对于体系的运行具有举足轻重的地位,直接关乎整个系统的性能优劣与稳定性、可靠性的高低。

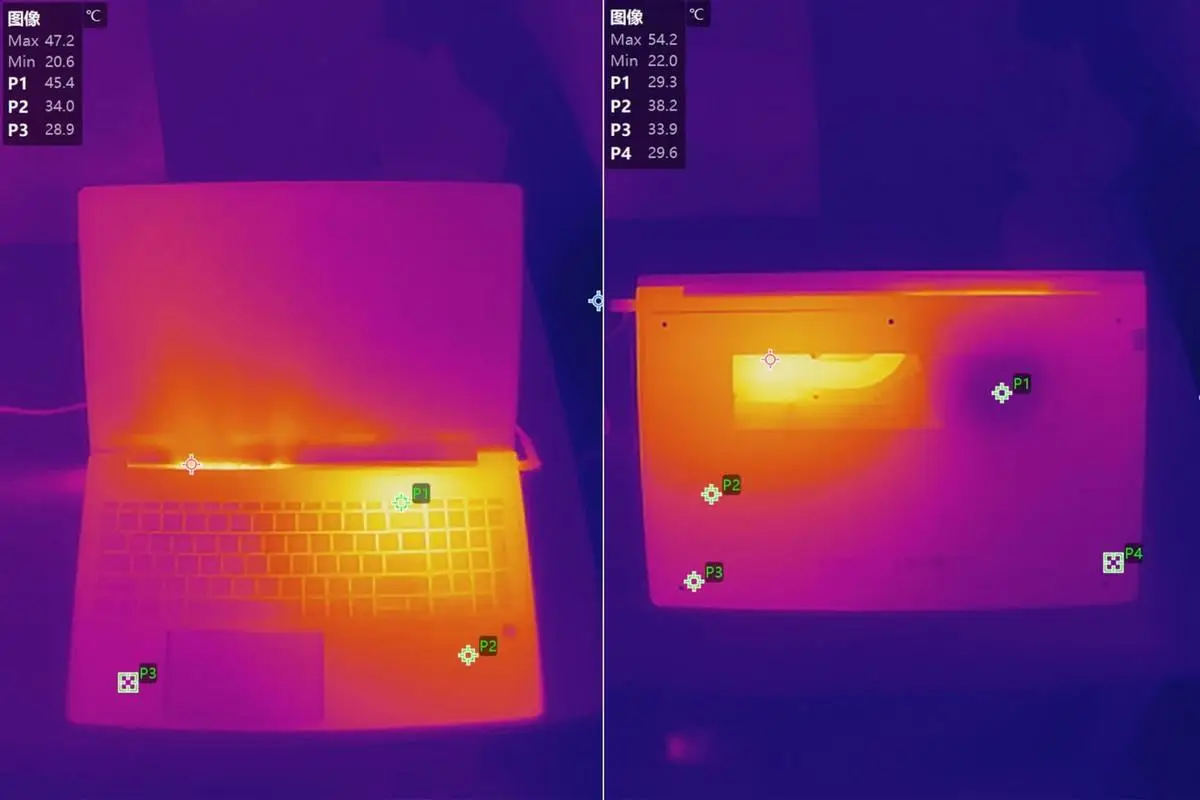

DDR SDRAM控制器与系统性能

DDR SDRAM控制芯片,这座構築在处理器与存储设备之間的橋樑,在很大程度上決定著整個系統的性能水平。一款高效率與穩定性兼具的DDR SDRAM控制芯片,能夠有效提高系統運行速度、減少能耗並不斷提升用戶體驗效果。但如果此設計上出現一些問題或其稳定性受到影響,則可能導致系統運行變慢乃至于經常性地關機、棄用等問題。

以提升系统性能为核心任务,优化DDR SDRAM控制体系结构至关重要。通过精准调整时间周期参数、精炼地址数据生成函数以及增强指令传递速率等措施,能显著加强DDR SDRAM控制器的效能及稳定性表现。同时,引进尖端且牢靠的误码侦测及修正机制,将有助于提升整个系统运行的鲁棒性。

随着大数据与人工智能技术飞速发展,对高性能计算具有更大需求。服务器、超算等将面临更高标准的DDR SDRAM控制器设计要求。因而,研发者们非常需要找到有效且稳定的方法设计此类控制器。

未来发展趋势

在科技持续攀升及应用领域日益扩张的契机下,DDR SDRAM控制器将展现如下重要发展方向:

在新型多媒体应用如4K/8K视频、VR和AR的广泛采用背景下,内存带宽的需求持续攀升。针对此趋势,DDR SDRAM控制器正向高带宽方向演进。

低能耗设计:伴随移动互联以及物联网的持续繁荣,对低功耗设备的需求日益旺盛。故而,未来的DDR SDRAM控制器将努力实现更加节能的设计,既提高性能又降低能耗。

稳定保障:鉴于当前网络环境下的安全风险不断加剧,未来DDR SDRAM控制器将进一步强化其安全防护措施,以提升数据的传输效率和精确度并全面保障数据安全稳定。

总之,鉴于科技日新月异以及应用环境日益广泛,未来DDR SDRAM控制器的发展充满无限潜力与光明前景。