什么是DDR布线

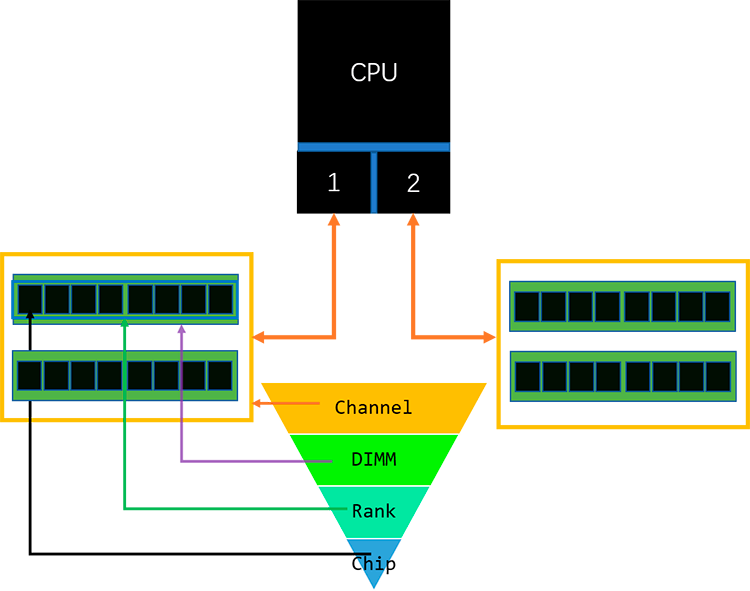

DDR(双倍速率内存)通过提升上下沿数据传输,实现高速运转。与之对应,DDR布线即为在设计电路板过程中,精心规划与布置内存模组至主板间信号路线,进而保障数据传输稳定且高效。作为现代电子产品中的关键要素,DDR布线对于系统性能具有实质性的决定作用。

针对DDR布线,首要关注点为保障信号完整性,这是避免信号在传送过程中的失真与信息丢失的重要手段。鉴于DDR的高速传输特点,对信号完整性的要求尤其严格。因此,设定合理的信号线长度、完成阻抗匹配和避免信号交叉及地线回流等方法在DDR布线上显得至关重要,此举有助于降低信号反射及串扰等问题出现的可能。

此外,在DDR布线过程中需充分考虑时序限制这一要点。时序制约即为设计电路板时要着重满足各项信号传输所需的时间,确保数据能准时送达至目的地。鉴于DDR因其高速运作及严格的时序需求,DDR布线时务必关注各信号的传输滞后情况以及时钟和数据对应关系等重要因素。只有满足这些时序规定,整个系统方具备正常运行的条件。

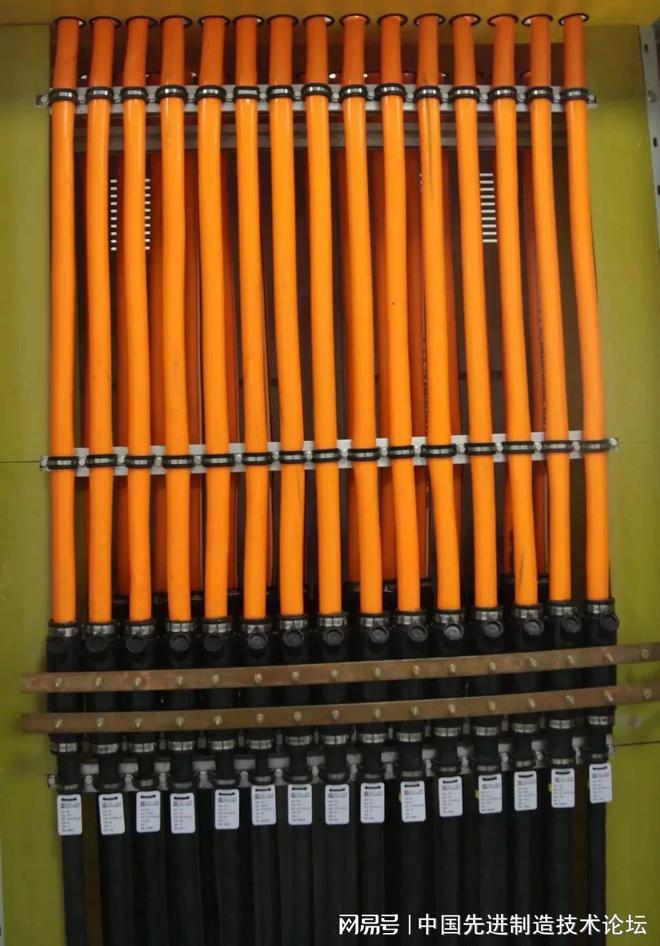

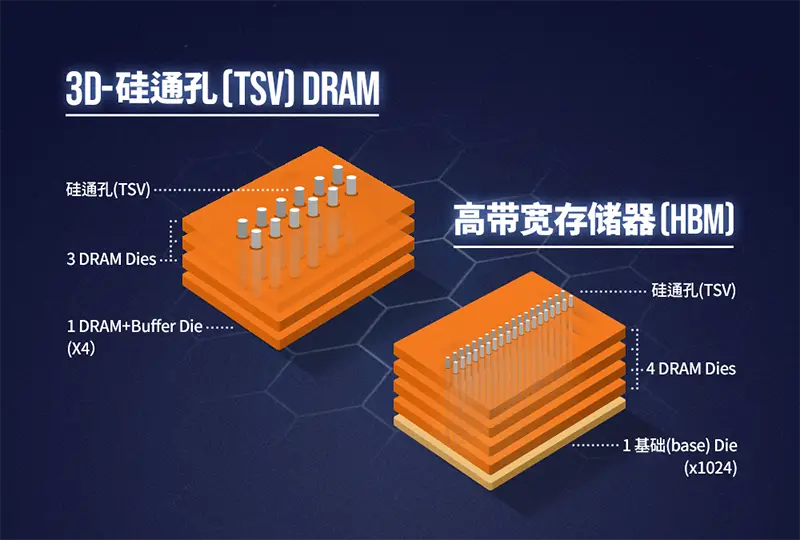

在此基础上,实施DDR布线过程中亦需高度重视功耗及热管理因素。伴随着芯片集成度与工作频率的日益提升,DDR内存组件的功耗也逐渐攀升,从而使得热管理成为至关重要的环节。因此,在规划DDR布线方案之际,须充分策划电力供给以及散热设计等诸多关键领域,确保整个系统长时间稳定高效运行。

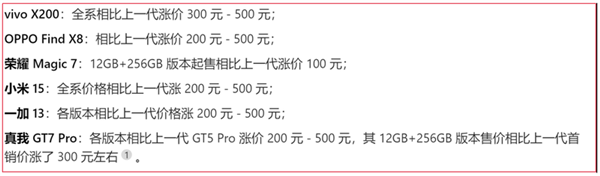

DDR3与DDR4布线实例比较

目前主流的内存标准包括DDR3以及更先进的DDR4,两者在布线设计上存在差异。前者由1.5V供电,频率范围在1600MHz到2133MHz内,而后者由于采用了1.2V的低电压,频率上限可达3200MHz以上。因此,设计时必须考虑以上影响因素。除此之外,两代标准还在时序约束及功率消耗控制等关键环节呈现出各自独特的特点。

以曾参于之一的服务器板设计项目而言,其已兼容DDR3与DDR4两种类型的内存条,且具备专属电源管理单元。DDR3与DDR4布线方面,我们运用了各自的层级架构及走向线路设计手法。针对DDR3内存通道,以保证信号质量和时序限制为主导,采取相对稳妥的设计方法;至于支持高频运行的DDR4通道,则选用精密得多的走线方式,并辅以电子模拟技术校验。

从具体实施的 DDR3 和 DDR4 内存布线项目中不难发现,因内存标准差异需拥有针对性方法,并依据现实环境作出相应调整。

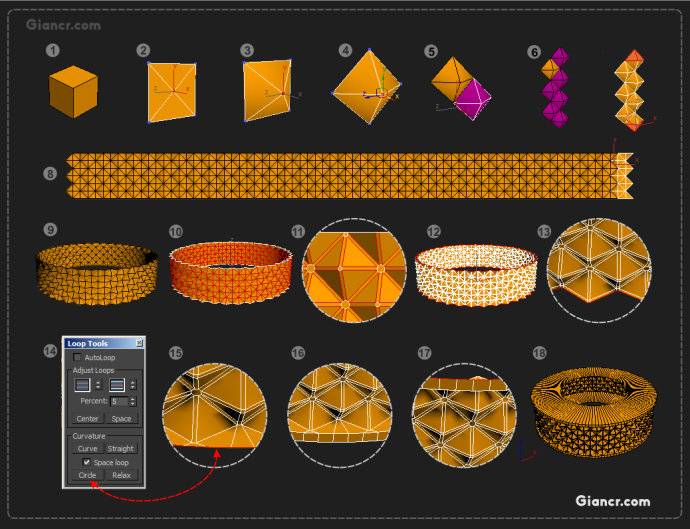

如何优化DDR布线

DDR布线优化措施有利于提升系统效能,降低能耗并消除电磁干扰。以下是几种常用的优化方式:

信号接驳:确保数据、地址、控制总线长度统一,防止延迟差异过大。

2.地引脚:使用地引脚填充空白空间可降低串扰。

3.交叉消除:避免数据/地址/控制总线交叉可减少干扰。

4.阻抗匹配:使用合适阻抗可减少反射并提高信噪比。

5.路由规则:遵循最佳路由实践可降低串扰风险。