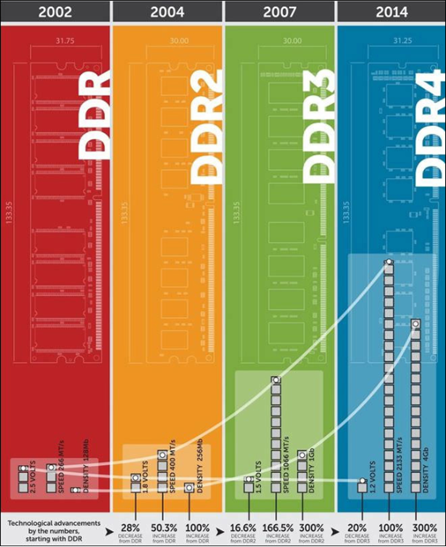

身为经验丰富的硬体工程师,我对DDR3 ECC校正技术有精深见解。本文旨在详细解析此项技术,涵盖定义、运作原理、应用领域、显著优点及未来发展趋势等元素。

1. DDR3 ECC校验的基本概念

首当其冲,我们需全面理解DDR3 ECC校验这一重要概念。DDR3为内存模块规范,EC具有Error Correction Code之含义,即纠错码。纠错码技术被嵌入至DDR3内存模块,以侦测及修正其中可能出现的数据错误。借助内存冗余信息存储,DDR3 ECC校验助力提升系统稳定性与可靠性。

当前主流的DDR3 ECC校验方法为单错纠错双错检测(SEC-DED)模式,此种方案能精确地定位与修复单比特错误,且具备检出(无法修复)双重比特错误的能力,从而有力地保障了系统在数据传输阶段受到各种错误干扰的情况下依然稳定运行。

在高可靠需求如服务器及工作站处,广泛采纳了使用DDR3 ECC内存这一技术,以确保系统稳定和数据无损。

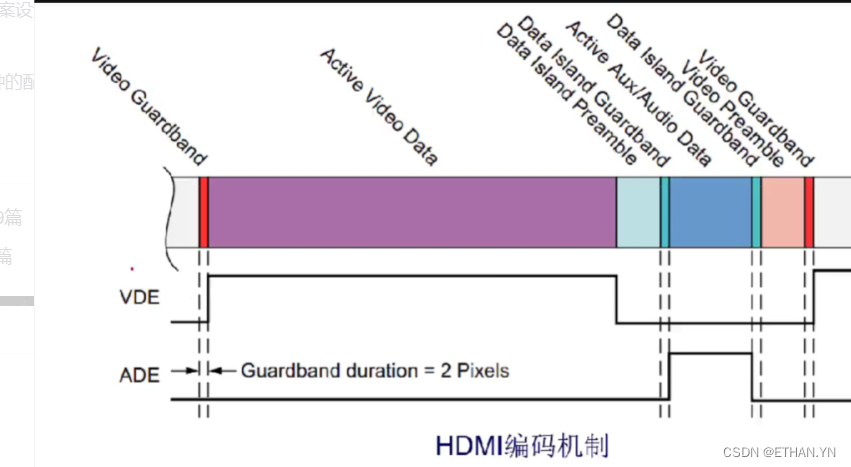

2. DDR3 ECC校验的原理

现在来深入分析一下DDR3 ECC校验技术原理。此项技术通过在内存模块内增设额外比特位得到体现。当数据被写入存储器模块时,相关软件将同步计算这些新增比特位,进而将其保存至内存之内。读取数据之时,系统程序将会重新演算这些新增比特位,并对照内存中原有的数值,这样可以发现并修复错误。

狭义地说,DDR3 ECC常用哈明码或伯勒-楚德汉姆码进行编码,增加了纠错补偿功能。这两种方法通过在原有的数据上加入冗余信号,从而达到精准识别和修正错误的目的。

除此之外,若传输过程中有单位错误发生,DDR3 ECC检验能运用额外的位进行自动修正;若碰到无法解决的多位错误,系统将触发警告机制,确保数据完整性的安全。

3. DDR3 ECC校验的应用领域

DDR3 ECC校验凭借其卓越的数据完整性防护性能,已广受各行业青睐并日趋成熟。

在服务器环境中,由于需维持长久稳固运作以及盛载大量机密数据,所以运用DDR3 ECC内存能降低硬件错误导致数据损毁的可能性,从而提升服务器系统的可靠性。

其次,在工业控制领域中,工业设备需长期稳定运作,数据精度亦有严格要求。使用DDR3 ECC内存能够抵御环境、电磁等多种干扰因素引发的数据错乱,确保工业设备的安全和可靠性。

在科学计算和金融交易等极度依赖数据精度的行业中,DDR3 ECC技术被广泛应用,用于保障数据处理过程零失误。

4. DDR3 ECC校验的优势

DDR3 ECC校验相比非ECC内存有着诸多优势:

首先,DDR3 ECC内存具备出色的数据纠错能力,能够及时检测并修正单比特位错误,大幅度提升了整个系统的稳定性与可靠性。

其次, DDR3 ECC可协助及时识别硬件问题并采取相应措施进行修复或替换,有效提升系统运行时间。

除此之外,DDR3 ECC内存具备出色的数据完整性防护性能,降低了由软件错误或者其它异常状况引发的数据受损风险。

总的来讲,利用DDR3 ECC技术能有效改善系统稳定性、延长硬件使用寿命及保护关键数据等多方面表现。

5. DDR3 ECC校验技术未来发展趋势

科技进步和市场需求驱动下,DDR3 ECC技术持续升级完善。

随着计算机应用范围与计算需求的持续增长,内存的稳定与可靠性显得日益重要。未来的版本有望提高ECC技术的精确度,使其应用于更多设备及环境之中。

随着数据科学中的自然语言处理和机器学习的快速发展,对计算机处理性能与精度的要求日益严苛。因此,为顺应新时代的需求,研发出更高级别的ECC技术解决方案势在必行。

展望未来,DDR3 ECC技术将不断致力于提升效能、精度以及全面性,以确保向各类计算机设备提供有力且稳定的支持。