1. DDR硬件电路设计概述

在当前数字化时代,DDR(双倍数据速率)内存已成为各类计算终端中的必备存储组件。其高速、高效率的特点使其在现代计算机体系中发挥着举足轻重的作用。DDR硬件电路设计作为保障DDR内存稳定运行的核心环节,涵盖了信号传输、时序控制以及能耗管理等多个层面,要求工程师对DDR内存的运作机制有深入理解并根据实际需求进行精细化设计。

DDR硬件电路设计的重点涵盖了内存控制器、数据线路布局、时钟管理及功耗优化等多方面。设计过程中需充分考虑信号完整性、严格遵守时序要求并兼顾功耗限制,以确保系统稳定高效运行。

2.内存控制器设计

内存控制具备衔接处理器与内存间的关键角色,主要负责协调数据传输及地址映射等功能,DDR硬件电路设计中,其设计具有举足轻重的地位。优秀的内存控制设计能提升系统性能,缩短延迟时间,确保数据精确无误。

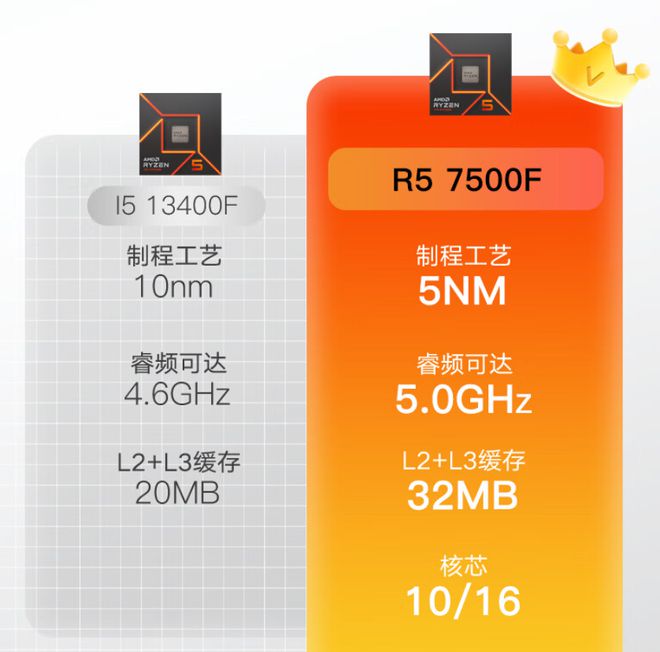

在内存控制器研发之时,务必关注诸多要素,如数据通道宽幅,指令序列调度及时序管控等。另外,依据实际运用环境筛选出适宜的内存控制器类型亦颇为关键,例如DDR3、 DDR4乃至日后更高级别的DDR规范均可选用。作为核心组件,内存控制器的设计需兼顾数据传输速率与能耗消耗以及热能散发等诸多因素。

3.数据线布线

数据线布线于DDR硬件电路设计具有举足轻重之地位。优良的数据线布局能显著减少信号传输延迟,降低串扰噪声,进而提升系统整体稳定性。在实际布线过程中,工程师需重点关注信号完整性及阻抗匹配两大关键因素。

科学设定数据线长度、采用恰当的差分对设置和运用先进的层间堆栈技术是独特性地优化数据线布局的关键方法。而在高速DDR接口配置过程中,差分信号传输技术的应用更是有效抵御噪声干扰,从而保证了数据传输的稳定性与可靠性。

4.时钟管理

时钟管理乃DDR硬件电路设计之关键要素。在DDR系统内,时钟同步为各零组件合作提供基础,恰当产生与分配时钟讯号能有效防范时序误差及故障。

在执行时钟管理的过程中,研发人员需关注主频选取、相位调整以及时钟缓存等关键环节。同时,在多通道DDR系统中,时钟同步问题亦不容忽视。通过科学制定时钟管理策略,可提升系统稳定性与性能水平。

5.功耗优化

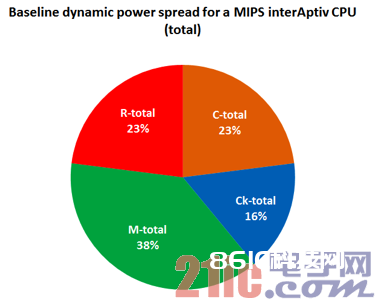

功耗优化,乃现代电子设备设计中的关键议题,其复杂性不言而喻。在DDR硬件电路设计领域,功耗优化的核心在于降低系统总能耗,从而延长设备续航能力。高效的功耗优化策略不仅能提升设备使用寿命,还可降低使用成本。

为实现功耗优化,可运用多种方法与技术如动态调频,睡眠模式配置及芯片级电源管理单元等。同时,实操过程中须针对特定场景进行精确的功耗调整,以达至最优性能与能耗平衡。

6.信号完整性分析

在DDR硬件电路设计中,保证信号完整性的重要性不可忽视,其能够防止数据传输出现误差或遗失,从而提高系统的稳定性与可靠性。

在执行信号完整性分析过程中,工程师需关注反射波干扰、串扰噪声及传输延迟等多重因素。借助仿真与实测方法,可对信号完整性进行评估,进而依据所得结果对电路进行相应的调整与优化。

7. DDR版本演进与未来展望

随着科技发展与市场需求的演变升级,DDR内存标准逐步发展,从初始的DDR1至当前主流的DDR4乃至可能出现的DDR5,各个世代DDR产品均具备更快速度、更大容量及更低能耗等优点。

伴随着新科技如人工智能、物联网的崛起,对更快的数据传输速率和更低的延迟的内存需求将持续增长。这意味着,未来的DDR硬件电路设计将面临更多创新技术和挑战。如何在提升性能的同时降低能耗,以及如何满足新型应用场景下的内存需求,将成为该领域的重要议题。