在现代信息化社会,计算机科技迅猛发展,各类硬件设备亦随之升级迭代。其中,DDR3内存凭借其稳定性强、性价比高的优势,得到了广泛应用。尤其是其搭载的ZQ校准技术,堪称性能卓越的关键因素。本篇文章将对DDR3 ZQ校准技术进行深度剖析,从基本原理到实际运用,为广大读者呈现这一引人瞩目的技术全貌。

一、DDR3内存基础

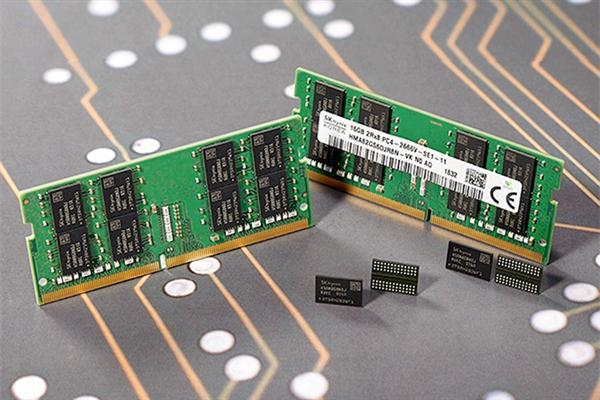

深入理解DDR3 ZQ校准前需先掌握内存知识。作为双倍数据速率(DRAM)同步动态随机存储设备,DDR3内存可以实施每时钟传输两次数据的操作,比基础版DDR2具有更卓越的速度与带宽,适用于各类计算机系统,如个人电脑、服务器及工作站等。

DDR3内存中的ZQ校准技术其重要性不言而喻。这一技术属于动态随机存取存储器(DRAM)的电气参数微调法,通过精准调整内阻值以提高电路信号的整体稳定性。而DDR3版的ZQ校准技术可视为其具象化实施,显著提升了内存的运行效能。

二、ZQ校准原理

ZQ校正技术着重于通过调整DRAM模组中的端子电阻值,实现与系统总线阻抗的精准契合,从而保证信号传输的顺畅及稳定。DDR3存储空间内的ZQ校正方式可分为动态与静态两大类。

动态的ZQ校准即是DRAM芯片在启动后或运转期间,根据系统环境改变对终端电阻作出相应调整。静态的ZQ校准则是出厂前已预设终端电阻数值,运行过程中无需再做调整。两种校准方法各具特点,可依据实际需求选用。

三、DDR3 ZQ校准流程

DDR3 ZQ精准调节流程主要包含三个阶段:初始阶段、训练阶段及稳态阶段。在初始阶段(系统启动或重置时),实施ZQ精确调参,并设定相关参数;然后进入训练阶段,此过程中终端电阻会根据实际需要实时调整至最适宜状态;最后进入稳态阶段,此时终端电阻保持稳定,保证了信号传输的高品质。

实践中,实现DDR3 ZQ校准需充分协调控制器、PHY层及其他关键组件,进行精密的时序管理及信号处理,以达到最佳性能表现。各部分协同配合至关重要,是保证DDR3 ZQ校准技术成功应用的关键所在。

四、DDR3 ZQ校准参数

在施行DDR3质量控制之ZQ精准校准过程时,需精心设定若干关键参数以指引及精进校正流程,这些参数包括ZQCS(ZQCalibrationShort)、ZQL(ZQLong)以及OCD(On-DieTermination)等。这些参数对ZQ校准的准确性与效率产生直接影响,在实际工程应用中需审慎权衡并适时调整。

除基础参数外,还需兼顾RTT(Ron、Roff及RttNom)和PARK等高端参数。这些参数间关系密切,需从多角度衡量,方能确定最优值。

五、DDR3 ZQ校准优化

为充分利用DDR3 ZQ校准技术优势,需实施多项优化策略。包括:精准调整ZQCS及ZQL参数,依据实际系统环境做出调整;改良OCD参数,提升信号完整性;以及对RTT与PARK等高级参数的精细调控,实现最优效能。

除此之外,我们还应深入加强PCB布线设计、信号线匹配与电源供应稳定性等多方面的优化工作,从而提高DDR3 ZQ校正效果。通过持续地对各类参数及设计策略进行精准细致的微调,我们能够有效达成最优质的性能表现。

六、应用实例分析

以服务器行业为参考,针对需追求高性能及稳定性的服务器体系,引入优质的DDR3 ZQ校准科技极为关键。通过专业设计以及精细调整,可确保服务器系统在需求压力过重时仍能保持稳定运作,同时提升数据交换速度。

此外,DDR3 ZQ校准技术亦被工业控制及通信设备等行业广泛采纳。凭借精确调整各参数并针对性地改进实践环境,该技术得以满足各类领域对内存性能及稳定度的高标准需求。

七、未来发展趋势

随着信息科技的蓬勃进步,DDR4和DDR5等新式内存产品逐渐崭露头角。为了适应这些新旧交替,新型ZQ校准技术也在持续革新中。展望未来,在高频率、大带宽需求日益增长的背景下,如何提高内存性能及稳定性将是重要的研究课题。