了解FPGA和DDR3

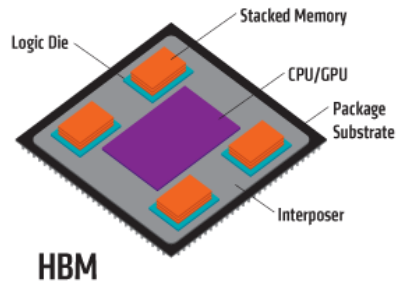

在深入研究FPGA与DDR3的带宽优化前,我们需科学理解其理论基础。FPGA(现场可编程门阵列)作为可编程逻辑器件,具备极高灵活度及强大运算能力,广泛运用于数字信号处理、通讯、图像处理等领域。DDR3(双倍数据速率第三代)则为内存技术标准,相较DDR2拥有更高速率和更大带宽,被广泛应用于各类计算机系统。

FPGA DDR3带宽概念

FPGA与DDR3内存间的通信带宽反映了其数据读取及写入速率与效率,它的优化直接影响到系统性能与数据处理速度,故成为工程师们关注的重点议题。无论是哪类应用领域,提升FPGA与DDR3通信带宽的效益都是极其显著的。

时序约束对DDR3带宽的影响

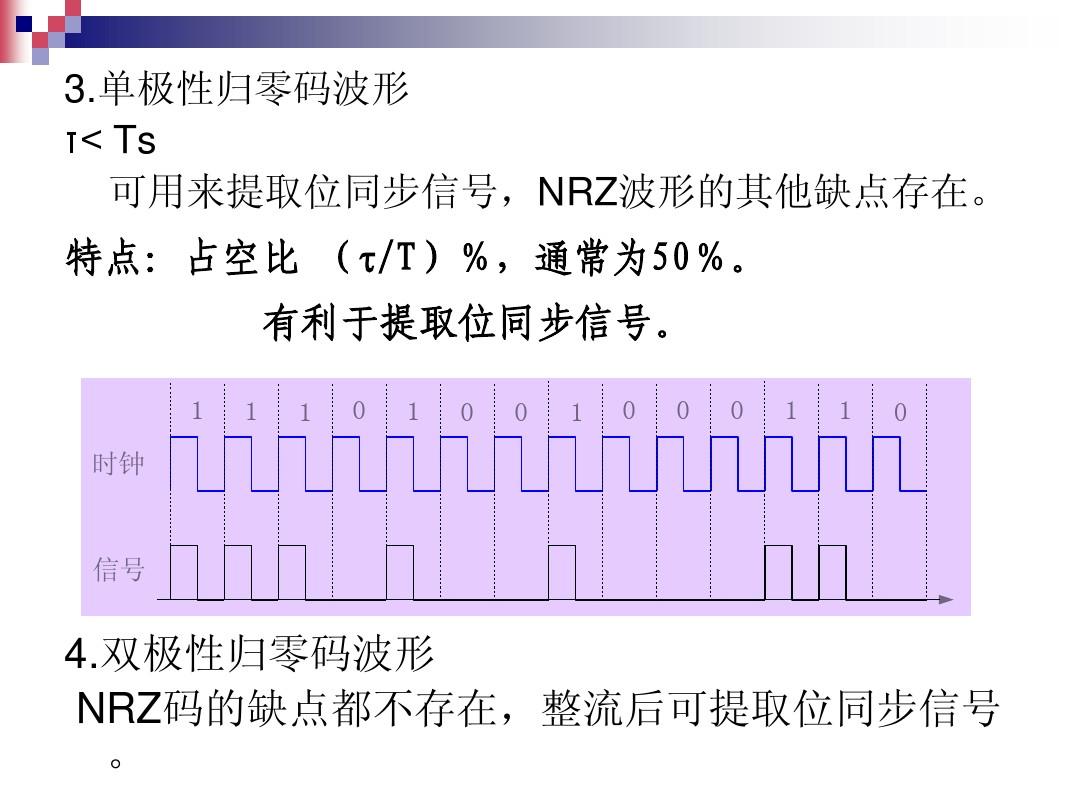

FPGA与DDR3接口的设计中,时序约束起着举足轻重的作用。它决定了数据传输过程中的时间规定,如时钟频率、延迟等参数。设定科学的时序约束可保证数据通信稳定可靠,进而提高DDR3带宽。

布局布线对DDR3带宽的影响

优良的DDR3数据传输带宽提升离不开精心设计的布局布线。PCB板上各器件的妥善安置、稳妥的布线和严谨的电源地线布置,将对信号传输质量产生直接影响。通过缩短信号传输距离、减少干扰等方式进行布局布线优化,可显著提高DDR3带宽。

信号完整性对DDR3带宽的影响

保证信号完整性的实现是提高DDR3带宽至关重要的环节。高速数据传输过程易受噪声和反射的困扰,进而引发信号失真乃至丧失。因此,设计阶段需着重考虑地线回流路径、阻抗匹配以及信号层堆栈设计等要素,以确保信号的完整性,从而最大化DDR3带宽。

时钟管理对DDR3带宽的影响

对DDR3带宽进行深度优化离不开对时钟信号的优化管理。时钟信号作为数据流动的同步标准,其设计过程中须考虑时钟的分配、缓冲区设定以及时钟树的构建等关键因素。通过科学地调整时钟网络架构及优化时钟分配方案,可显著提升DDR3的带宽性能。

功耗优化与DDR3带宽

衡量系统性能稳定的关键因素包括功耗。在优化DDR3带宽时,需着重权衡能耗与性能之间的平衡。运用低功耗设计及动态电压调控等策略,可确保系统稳定性同时提高DDR3带宽。

综合考虑因素优化DDR3带宽

总结地说,在实际设计过程中,我们需全面兼顾时序约束、布局布线、信号完整性、时钟管理及功耗等各项因素,从而提升FPGA DDR3带宽的性能表现。唯有精确把握上述关键要素,并结合实际需求进行适当调整与平衡,方能达到最优的DDR3带宽优化效果。