DDR的PHY(物理层),作为DDR(双倍速率)内存的关键部分,承担了在内存控制器与内存颗粒间进行数据传输的重任。本篇文章将对DDR的PHY进行深度剖析,内容涵盖基础理论至运行机制,再到性能提升及未来发展方向等方面,旨在为广大读者提供关于DDR内存技术的全方位解读。

1.DDR的PHY简介

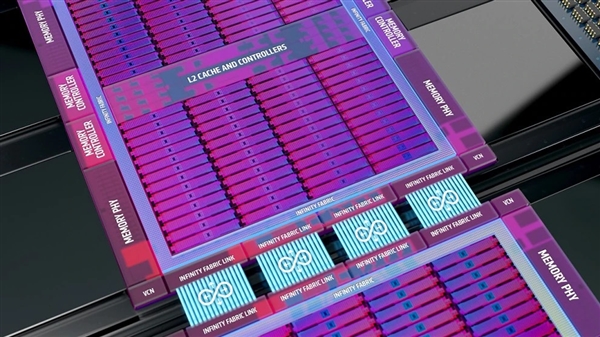

在内存系统中,DDRPHY充当关键角色,负责处理控制器与DDR内存间的数据流通。此设备为物理层的一环,承担着信号调节、时序管控及数据缓冲等多重职能,从而对内存系统的性能和稳定产生直接影响。

DDR内存采用双倍速率传输技术,每时钟周期能进行两次数据传送。因此,DDRPHY需要能够精确捕获并处理来自内存控制器的指令,然后将数据高速传输至内存芯片,确保数据的准确性与稳定性。

2.DDRPHY的工作原理

DDRPHY的运作原理关乎诸多要素如时钟控制、数据对齐以及时序校准等环节。其中,时钟控制构成了DDRPHY的基石,其主要功能在于确保数据的同步传送。而数据对齐则是为确保内存控制器与存储芯片间的数据交换的准确无误,通过精准的时序掌控及数据缓存机制得以达成。

此外,DDRPHY还需进行时序校正,以消除信号传输中可能出现的时序偏差及抖动。这项工作需要精确的电路设计与优秀的算法优化,保证数据传输的无延迟稳定可靠。并且,DDRPHY还应兼容各类时钟频率和数据传输模式,满足多样化应用场景的实际需求。

3.DDRPHY的性能优化

为提升DDR内存系统效能,DDRPHY的精妙设计与深度优化尤为关键。首要任务即优化DDRPHY电路,采用尖端制造工艺及高效电子元器件,从而提升信号传输速率与稳定度。

其次,时序参数及数据传输策略的调整,能够有效提升DDRPHY的性能表现。例如扩大数据缓存区域、精进时序校正算法以降低时序抖动与延迟,从而提升数据传输速率与稳定性。

借助于提升DDRPHY的时钟速率与数据容量,可较大幅度地增强内存系统效能。运用高速时钟及数据总线,便可达成更快的数据传输速度与更大的带宽,从而适应不断升级的应用需求。

4.DDRPHY的未来发展趋势

伴随着计算机科技日新月异的进步,DDRPHY也在持续演变与革新。展望未来,DDRPHY将致力于能耗与性能的完美结合,运用尖端的节能技术以及深度优化的电路架构,从而提升内存系统的能效比及性能密度。

同时,DDRPHY将支持高速的时钟频率及大容量的数据传输带宽,满足日益攀升的数据处理需求。采用新型信号调制策略与数据传输协议,DDRPHY的效能与可靠性得以大幅提高,数据传输更为迅速且稳定可靠。

在此基础上,DDRPHY将更加侧重于与其他硬件部分的协同规划及性能优化,进而全面提升存储系统性能。通过与处理器、芯片组等主要硬件相互协作,可显著提升系统性能并加快响应时间,更好地适应各类应用场景需求。

5.结语与展望

DDR的PHY作为内存系统关键组件,对计算机科技进步起着关键影响。深入理解其基本原理与操作流程,有助于提升内存系统性能及稳定性,推动数据高效传输及处理进程。

随着科技持续深化及应用领域的扩展,DDRPHY将继续承载重任,引领内存科技的发展与突破。期望DDRPHY在未来的成长道路上愈发成熟,为计算机系统性能提升以及应用范畴的扩大做出更显著的贡献。

对于DDRPHY的观察,您觉得如何呢?关于其未来发展前景,您又有何预计?期待您的分享与探讨。