伴随着科技进步与升级,计算机领域的硬件产品也在不断推陈出新。其中,内存模块作为计算机体系的关键组成部分,其性能及规格对于整体系统的效率与稳定起到决定性的作用。目前市场上流行的DDR6与DDR5内存标准,其脚位图设计直接关联着内存模块的性能表现以及兼容性问题。本篇文章将详细解析DDR6与DDR5的脚位图设计及其相关知识,以期为广大读者提供关于这两种内存标准的全面理解。

1.DDR6和DDR5脚位图概述

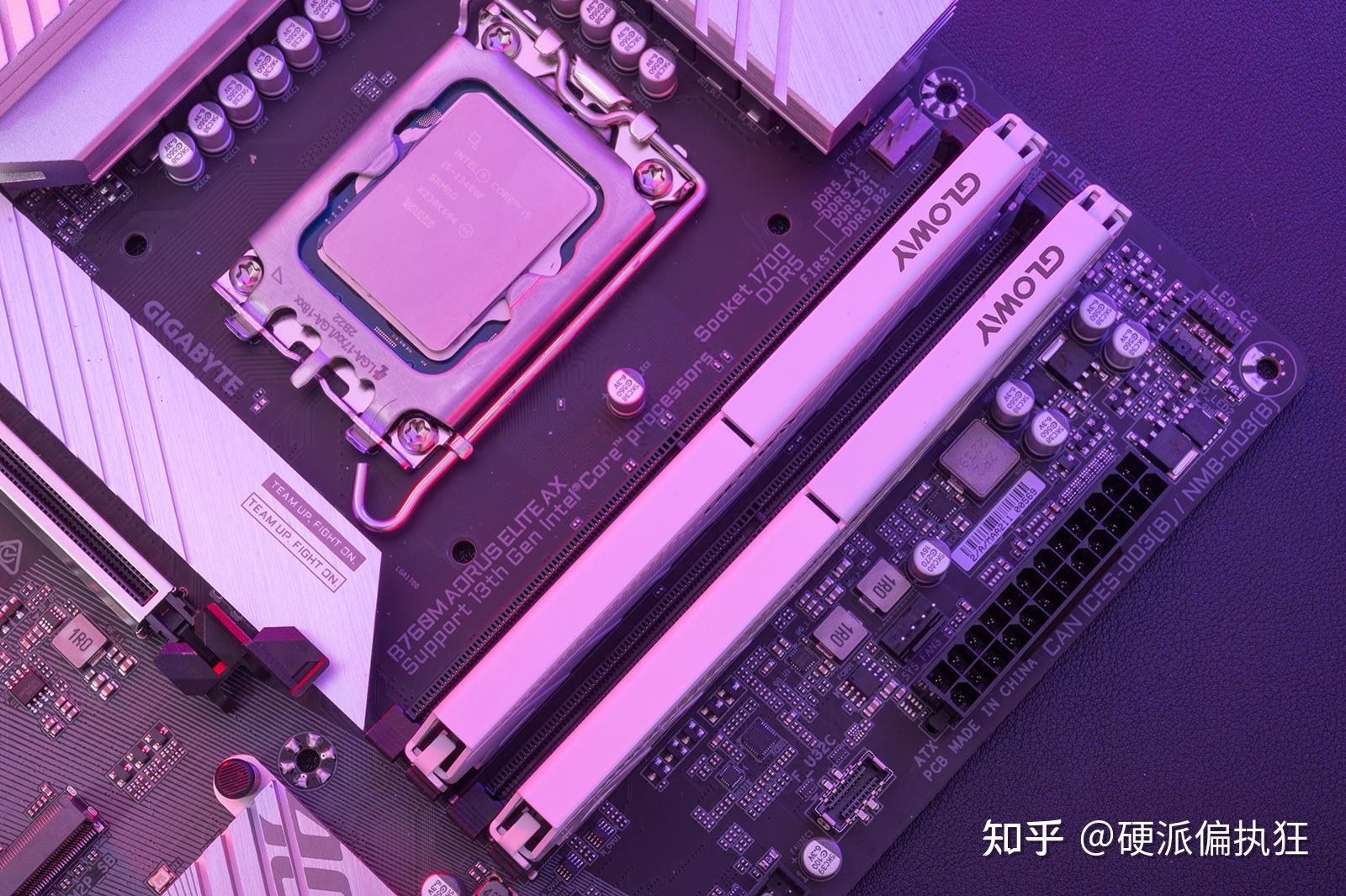

DDR6和DDR5作为最新一代内存标准,脚位图设计直接影响着内存模组的性能与兼容性。脚位图即是内存模块与主板插槽间金属接点的布局图表,涵盖了电源供应、讯号传递及时序掌控等重要功能引脚。与先前的DDR4标准相比,DDR6和DDR5的脚位图进行了显著改进,优势主要表现在:

第一,脚位数与布局愈加紧凑且精炼。受工艺技术提升之助,内存芯片集成度日益攀升,DDR6及DDR5模块能以更小体积获取更高容量与带宽,故而脚位数相较DDR4有所削减,然而功能性则更显卓越。

其次,供电与信号传输设计更为稳定且高效。DDR6及DDR5内存模组在脚位图设计中增强了电源与信号处理功能,通过优化供电引脚布局以及信号传输路径设计,提升了内存模组的稳定性与抗干扰性,进而提升了整个系统的性能与可靠性。

最终,经过对时序控制与数据传输的改进后,DDR6及DDR5内存模组得以更精确、高效率地操控数据的读取、写入与传输过程,从而显著提高设备响应速度以及数据处理能力,以应对不断增长的计算需求。

2.DDR6和DDR5脚位图设计的关键技术

DDR6与DDR5内存模块的脚位布局需运用众多关键科技。

2.1高速信号传输技术

鉴于内存频率逐步升级,为确保DDR6与DDR5内存模块性能稳定可靠,脚位布局需兼顾高速信号的传输。差分信号传输、串扰抑制以及时钟信号优化等,均是高速信号传输的关键技术,通过对它们的优化,便能在保障信号质量的基础上提高数据传输速度。

2.2供电和地面引脚设计

DDR6及DDR5模块在供电与地脚设计方面尤为关键,直接关系到其稳定与能耗表现。设计过程中需保障供电路径简短高效,同时注意地面引脚合理布局,有效降低供电噪声以及电磁干扰,从而提升系统稳定性与可靠性。

2.3时序控制和数据路设计

在DDR6与DDR5内存模块的Pinout规划中,需注重时序控制及数据通道的设计。此举关联至内存控制器与存儲晶片间的数据交互及其时序协同。通过精进时序控制与数据通道的设计,可降低数据传输的延迟并减少时序抖动,从而提升内存模块的读写效率与稳定性。

3.DDR6和DDR5脚位图在实际应用中的意义

DDR6及DDR5内存模组的引脚布局设计不仅关乎理论研究,更与实际运用紧密相连。在实践操作中,引脚布局的优劣直接决定了内存模组的性能、稳定度以及兼容性,从而对整体系统的运作效能和用户体验产生深远影响。

先进的脚位图设计能显著提升内存在运行过程中的性能表现及数据吞吐速率,进而显著改善整套系统的整体性能与反应速度。

再次强调,稳健的脚位设计能提升内存模组乃至整个系统的稳定性与可靠性,降低因蓝屏、死机等问题而导致的系统故障几率,确保系统长时间稳定运行。

最终,优化且适用的脚位设计能保证内存模组与主板及其它硬件设施的协调工作,从而减少硬件间并发冲突以及兼容性问题,提高了整体系统的可靠性与稳定性。

4.结语

总结而言,关于DDR6与DDR5内存模块脚位图设计的深入探讨,无疑在内存技术领域占据了重要地位,且对改善系统性能、增强稳定性和提高适用性有着举足轻重的影响。展望未来,伴随着科技日新月异以及内存需求持续攀升,我们有理由期待DDR6与DDR5脚位图设计将继续推陈出新,为计算机系统的发展注入新的活力和机遇。

敬请关注,对于DDR6及DDR5内存模组引脚图设,您是否有独特观点或建议呢?欢迎留言互动交流。