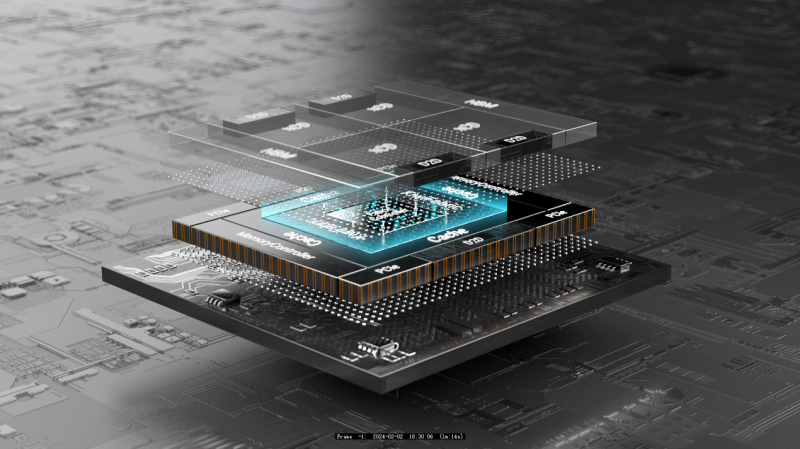

当前,DDR(双倍数据速率)内存已广泛应用于各式电子设备。其性能及规格直接影响了整个计算机系统的表现。因此,在设计与配置计算机系统时,我们需充分重视并理解DDR内存地址位宽的计算。本文将系统梳理DDR地址位宽计算的相关知识。从基础概念到具体实践,助你轻松掌握DDR内存地址位宽的计算方法。

1.DDR内存简介

DDR内存乃高性能动态随机存取存储器(DRAM),较传统SDRAM更为快速,因每时钟周期可实现双倍数据传输。该内存主要包括四大系列:DDR1、DDR2、DDR3及DDR4,各版本性能与能耗均有差异。然而,无论何种版本,地址位计算皆为关键所在。

2.DDR地址位数概述

DDR内存的地址位数是其寻址能力的关键因素,它直接影响着内存的最大容量。地址位数越多,对应的内存容量就越大。通常情况下,DDR内存的地址位分为行地址位与列地址位两个部分。行地址位决定了内存的行数,而列地址位则控制了每行中存储单元的数量。通过将行地址位与列地址位相结合,中央处理器(CPU)便能精确地定位并访问内存中的每个存储单元。

3.行地址位数计算

内存行地址位位数判定依据为芯片组合与密度。在DDR内在中,其调节行地址位数可设立存储单元行数,一般被内存控制器依据特定的内存架构加以设定。

在DDR内存芯片中,每行的地址位数可依据如下公式进行核算。

根据公式,行位数等于以二为底的行大小除以行粒度后取对数。

"其中,"Row_Size"代表每行数据字节数,而"Row_Granularity"则为行粒度单位。此项指标由内存控制模块及芯片规格共同界定,从而明确了内存行的固定长度。

4.列地址位数计算

列地址位数的计算源于内存芯片的构造和容量考虑。它限制了每行内存域的大小,即每一个存储单元所包含的列数。如同行地址位数,列地址位数亦经由内存控制器设定,并依照特定的内存规范进行微调。

DDR内存单片的列地址位数可由如下公式得到:

[算式:Column_Bits=log2((Column_Size)/column_granularity)]

在此描述中,\[Column\_Size\]代表各列尺寸,\[Column\_Granularity\]则代表列级颗粒度。此项亦与内存控制器及芯片规格紧密关联,用以确定内存列之宽度。

5.地址位数与内存容量的关系

DDR内存的地址位宽直接决定了其寻址能力及存储容量上限。通过调整行地址位宽与列地址位宽,能实现多种不同规模的内存结构设计。如加大这两方面的长度,便能相应地扩展内存中的行数列数,因此达到提升存储容量的目的。

6.DDR内存的配置与优化

在实际运用中,DDR内存地址位宽设置需依据系统需求及性能需求进行精准优化。科学的地址位宽设定可提升内存在系统中的访问效能与整体性能。故而,设计与配置计算机系统过程中,务必全面考量DDR内存地址位宽计算,并根据实际状况进行相应调整与优化。

7.DDR地址位数计算的挑战与发展

随着计算机系统及存储技术的发展与革新,DDR地址位数计算亦面临诸多挑战。如内存容量增长导致计算与配置日趋复杂;新型DDR内存及其相关技术的出现,进一步增添了解决此问题的难度和机遇。

8.结语

在设计与配置计算机系统时,DDR地址位宽的精确把握具有至关重要的影响。深度理解DDR内存地址位数的计算法则及方法,能为系统的精细调整与优化提供有力支持,进而提升系统的整体性能与稳定性。期望本文能为广大读者揭示DDR地址位数计算的奥秘,并在实践操作中发挥其价值。