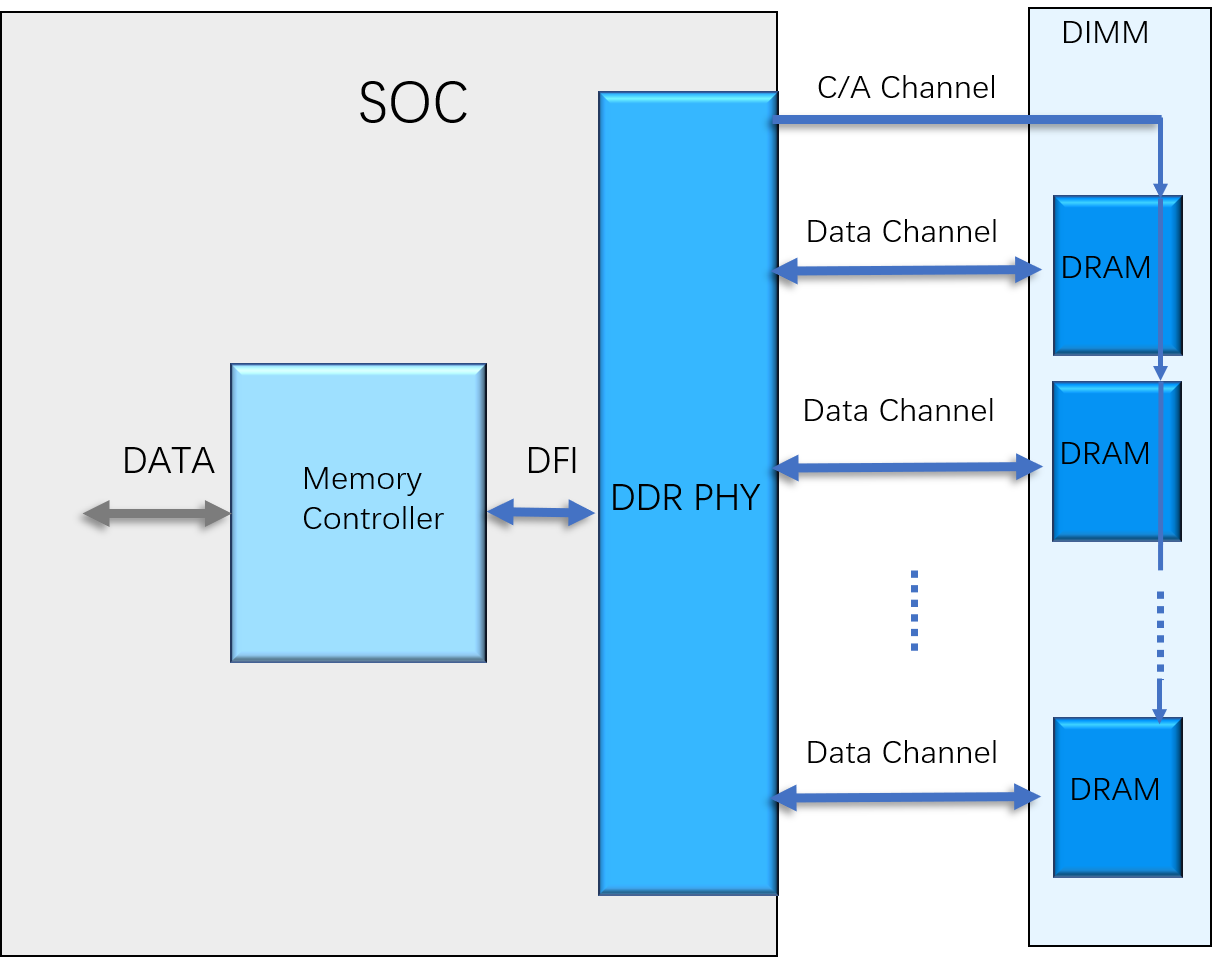

在讨论DDR(双倍速率)内存等长话题前,须明白DDR内存运作原理与构造。DDR内存作为计算机系统的随机存储器(RAM),具备在时钟信号上升与下降沿均可传输数据的特性,较之传统SDR(单倍速率)内存,能够显著提升传输速率。因此得名“双倍速率”。在计算机科学中,内存等长的重要性不言而喻,特别对DDR内存来说,其等长性直接关系到系统的稳定及性能表现。那么问题来了,DDR内存又是如何保证等长性的呢?以下将详细解析。

1.内存等长的概念

在计算机体系结构中,对称性即数据传输过程中的时间长度相似。以DDR内存为例,因其具备双倍数据传输速率的特点,保持数据传输的对称性显得尤为关键。若数据传输时间不均,将引发读写错误,进而影响系统稳定与性能。因此,在DDR内存的设计与实现过程中,必须充分重视对称性的保障。

实现在DDR内存等长要求需多方面兼顾,主要包括信号传输路径长度、延迟及时序控制。唯有全面精准调控以保证数据传输始终等长,方能提升系统稳定与性能表现。

2.信号传输路径的设计

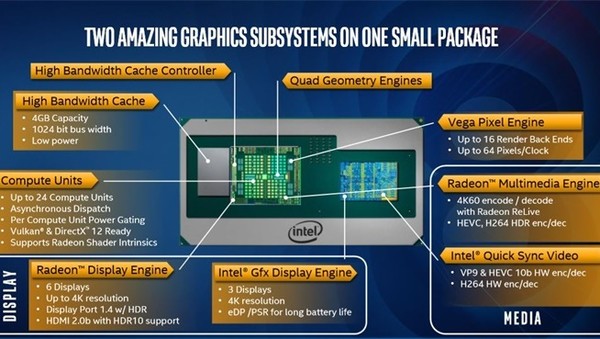

DDR内存信号传输路径的设计对其等长性能至关重要,常选用对称的芯片排列策略来保证各通道长度相同。同时,印刷电路板(PCB)设计需兼顾信号质量,运用合理布线及层间间距调整,尽可能缩小路径差异,进而达成等长传输效果。

不仅如此,针对高速信号传输,理解并妥善处理信号的反射及干扰势在必行。故此,在设计DDR内存时,需采纳多种策略以降低信号反射与干扰,如采用终端电阻和精心设置信号引脚布局等途径,以确保持续稳定可靠的信号传输过程。

3.时序控制的优化

在信号传输路径规划之外,时序控制也对DDR内存等效长度产生关键性影响。其关注的核心在于,通讯协议和时序参数的设定须确保内存控制器与DDR颗粒之间顺利沟通,主要涵盖时钟频率、时序延迟及时序间隔等要素。

为了保证DDR内存数据传输过程中的等长特性,需适度调控其时序参数。这不仅涉及到内存控制器的时序调整,更重要的是对DDR内存颗粒自身的时序设定进行精细化调度。时序掌握精准,方能保证DDR内存的等长特性,进而提升整体系统的稳健性及运行效能。

4.器件匹配和校准

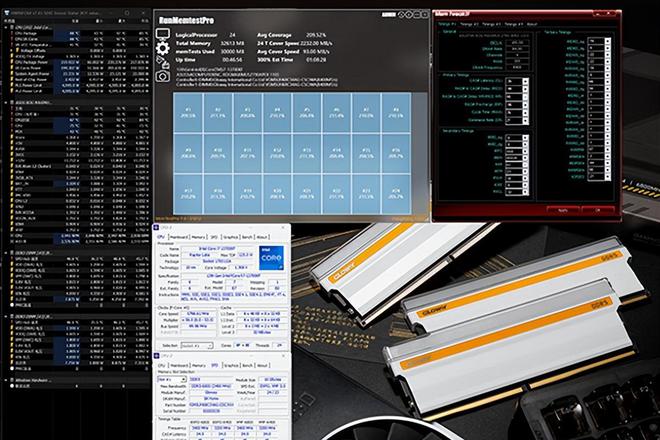

鉴于制程工艺与器件特性的多变性,使得各款DDR内存间难免存在差异。为确保系统稳定高效运转,DDR内存芯片需经过精确匹配及稳定校准。

器件配对即在系统设计与制造环节挑选同批次、同类型规格及参数的DDR内存组件,力求降低各部件间的异质性。另一方面,器件校正则是利用软硬结合的技术,于系统启动与运行阶段对DDR内存元件进行调试与矫正,使其适应当前工作条件与应用情境。

通过调整及校验装置的配合,能够有效提升DDR存储系统中的等长性,从而增强设备稳定性与性能指数,使所传输的数据更为可靠且精确无误。

5.内存布局和排布

在精心设计信号通道和调整时间顺序之余,合适的内存分布与排列亦对DDR内存的相等长度起着决定性作用。理想的布局及排列方式能缩短信号通路的长度差值,进而提升系统可靠性和性能表现。

在计算机系统设计时,常将DDR内存模块置于平衡位置,降低信号传播距离差异。此外,设计内存通道并安排其结构也至关重要,保证数据流等长,从而提升整个系统性能。

6.电气特性的调节

在DDR内存研发及调优环节,电子特性调整至关重要,如电源供应电压、信号幅度及信号波形等因素。精确把握并调整这些特性,有助于提升DDR内存的长期稳定性,保障档案传输与读取/写入过程中的准确无误。

在调整DDR内存芯片电气特性时需全面权衡其规格及要求,结合实践应用背景与环境因素。唯有精准调整参数,方可保障内存稳定高效运行,提升整个系统的可靠性及实用性。

7.测试和验证

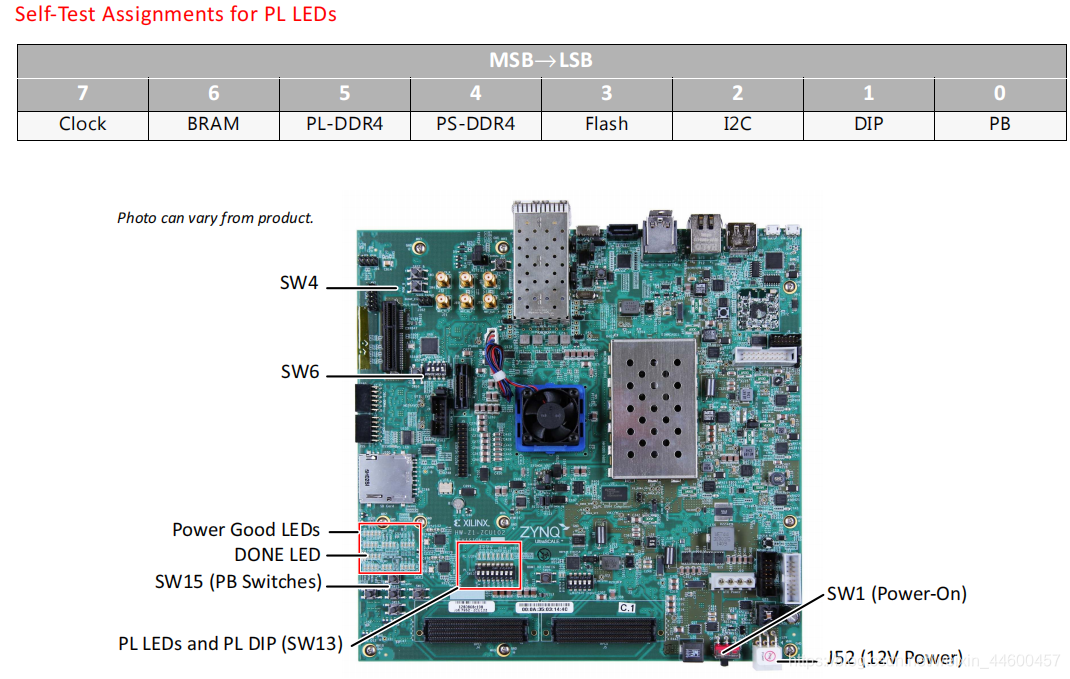

最后,为保证DDR内存等长性之有效执行,务必依照要求完成全面的测试与验证流程。在DDR内存的设计与生产全过程中,须严格执行各项测试与验证程序,如原型设计阶段、样品验证阶段以及大规模量产阶段均需包含在内。

借助严谨的测试与验证流程,我们可迅速察觉并排除DDR内存长期运作中的潜在问题,确保其在实际应用场景下能完美符合设计标准及性能预期,进而有效提升系统的稳定性与可靠性,保证数据的安全性及准确性。