作为一位资深工程师,我日常工作中的主要任务就是进行DDR线序的调整。本文旨在深入解读这一重要技术环节,并分享实际操作过程中所遇到的挑战与解决策略。

理解DDR线序调整

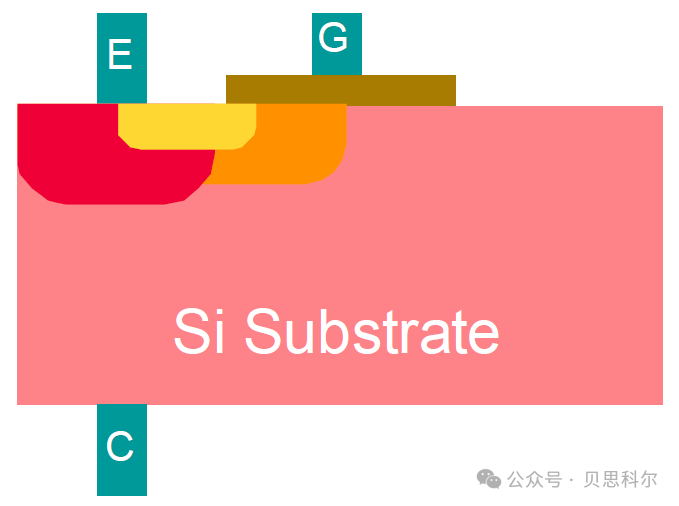

DDR线序调整即是通过设计PCB板并调整其传输信号,以保证数据存取在内存中的按序进行,进而提升系统稳定性及性能。此举对于高速电路设计尤为关键,直接关系到系统运行速率与稳定度。

在执行DDR调序操作过程中,务必充分关注传输延迟、时序关联以及信号完整性的问题。通过科学的布线设计与参数微调,确保数据能在内存芯片与控制器间精准传递,从而规避时序故障及数据误差的发生。

挑战与应对

在实际工程领域,DDR布线顺序调整过程需面临诸多挑战,尤其信号完整性问题突出。高速信号在传输路径中容易遭受噪音与干扰影响,致使信号失真及时序错乱。为此,必须采取相应解决策略,如优化布线布局、增设终端电阻、降低信号反射等方式,以实现信号稳定传输。

另一项重要挑战在于时间序列分析及优化。DDR线序调整涉及到的繁复时序关系,需要准确计算并把握每一信号的延迟及其时序关系,确保各信号按预定顺序抵达目的地。若遭遇时序失谐或频率未达标等状况,我们需依循调整布线、变更参数等方式进行优化,以符合设计需求。

实践经验分享

在长期实践与探索中,本人对于DDR线序调整形成一定心得。为提升效果,建议合理布局内存及控制部件,缩短数据传输路径。同时,选用适宜的PCB层数及材质,有效减少信号传输损失及干扰。此外,持续升级设计工具与参考资源,紧跟行业前沿技术动态,同样对于提高DDR线序调整能力大有裨益。

未来展望与思考

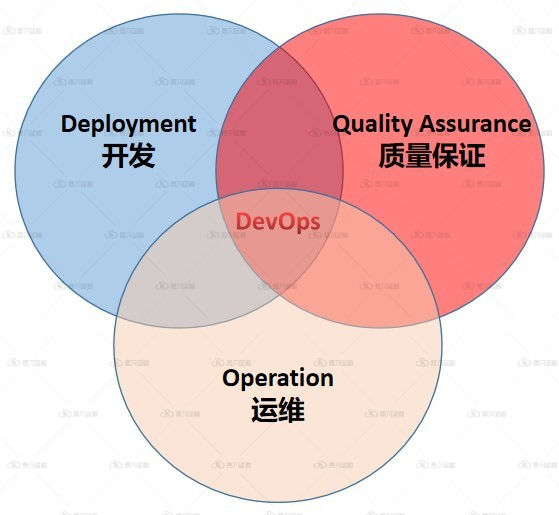

伴随着科技进步,DDR线序调整方法正逐步发展革新。展望未来,运用如人工智能及大数据分析等尖端技术,有望实现对DDR线序调整流程及方法的深度优化,从而提升其效率与精确度。同时,我热切期望能与业界同仁共同研讨交流,共享经验,以期携手推进DDR线序调整技术的创新发展。

结语

高速电路设计中的DDR线序调整具有关键意义,对系统性能与稳定有着直接影响。实际操作过程中,我们必然会遇到各类难题,而这些难题恰恰推动了我们持续努力并不断提高水平。随着科技的快速进步以及我们经验的日益丰富,有信心面对各类挑战,为电子产品的推进做出应有的贡献。

在处理DDR线序调节的过程中,您有何高招来克服困难?希望能听听您独特的实践经验及专业洞见。期待您在评论区分享宝贵心得!