身为计算机硬件工程师,我深感DDR线速测试之挑战性与重要性。DDR(DoubleDataRate)内存已成为现代计算机系统中的重要组件,而DDR线速测试无疑是保障其稳定性能的关键环节。本篇文章将详细论述我在此领域的经验及观点,共同探索DDR线速测试的神秘面纱。

1.DDR线速测试概述

首当其冲,请允许我们深入剖析DDR线速测试的核心内容。该测试主要通过操控内存模组完成读写操作,检验其数据传输速率及稳定性,旨在保证内存模组在重压环境依然能够稳定运作。相关测试环节涵盖了时序分析、信号完整性检测以及噪声干扰解析等多方面,需借助专业设备与软件辅助执行。

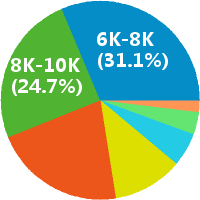

在实施DDR速度测试环节中,需重点关注内存模块的频率、时序特性及传输带宽这几项核心要素。精确把握并调整这些因素,以适应实际使用环境进行实验验证,将有助于全方位衡量内存模块的整体效能。唯有经过严谨的速度测试,方能保证内存模块在多重负荷条件下保持稳定运行,从而为计算机系统提供坚实保障。

2.DDR线速测试方法

在DDR线速测试中,可选用逻辑分析仪、波形发生器和信号发生器等仪器来解决问题。逻辑分析仪能捕捉并剖析内存模块的信号波动,检测潜藏的时序问题;而波形发生器以各种频率与时序需求生成数据模式,用以检验内存模块在各类操作环境中的效能表现。

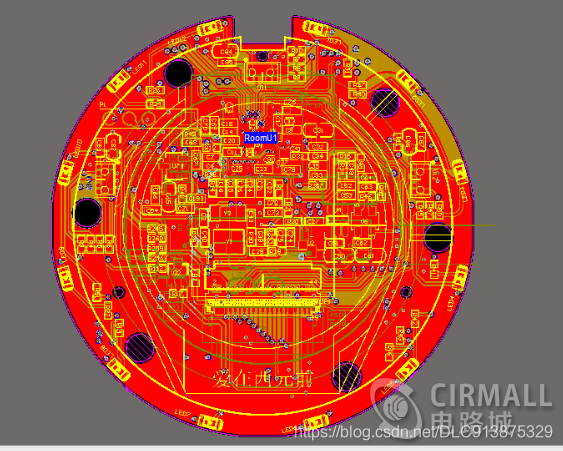

除了硬件工具之外,许多专业软件也可协助DDR线速测试。这类软件通常具备可视化界面,支持各类标准及定制化的测试过程,同时生成详尽的报告与分析结果。将两者有机结合,不仅提升了测试效率,而且能够有效快速地检测并解决相关问题。

3.DDR线速测试挑战

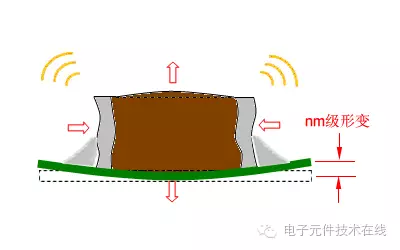

在实施DDR速度测试的过程中,经常面临众多挑战与难题。例如,高速稳定测试需关注信号完整性与噪声干扰;而性能评估则须兼顾数据传输带宽与延迟等多重参数。

在多通道DDR系统实施线速测试的过程中,面临着诸多难题,其中包括各通道间的相互影响及干扰,这无疑增加了调试工作所需耗费的大量时间与精力。因此,如何在多通道系统环境下高效解决问题便成为了DDR线速测试中的关键议题。

4.DDR线速测试应用

即便DDR线速测试面临诸多困扰,但是它在实际运用中的关键地位不容忽视。对于各类电子产品如计算机服务器、网络设备以及嵌入式系统来说,实施严谨的DDR线速测试是必不可少的环节,用以检验它们的内存子系统是否达到了预期设计标准,确保整个系统能够稳定工作。

须注意的是,诸如物联网、人工智能等尖端领域,对内存性能及稳定度有着更高标准。在此背景下,DDR的线速测试变得至关重要,其需通过持续优化以适应不断提升的应用需求。

5.DDR线速测试未来展望

随着计算机科技的持续突破,DDR内存亦不断革故鼎新。伴随着DDR5、LPDDR5等前沿存储规范的广泛采纳,对DDR数据传输速率的检测工作亦需随之提升。面对新技术所带来的挑战与机遇,我们需持续深化技术研究,保持行业动态,以从容应对。

随着人工智能与大数据领域的繁荣,对高效能、低能耗内存的需求日益迫切。预见未来,DDR线速测试领域将涌现更多创新技术及方案,为计算机系统稳定性提供有力支持。