身为科技热忱攻城狮,我深度钟情于研究Zynq的串口读写DDR功能。Zynq乃Xilinx精心打造的SoC芯片,融合了ARM处理核心及FPGA技术,具备卓越的运算性能和高度灵活性。其中,串口读写DDR功能便是其在数据传输与存储方面的关键应用之一。借助此项技术,我们得以实现数据的高速传输,并进一步拓宽Zynq在各行各业的应用空间。

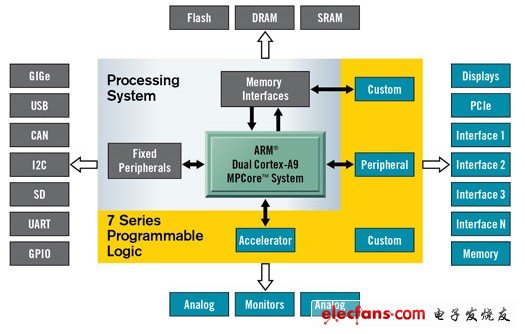

1.理解Zynq架构

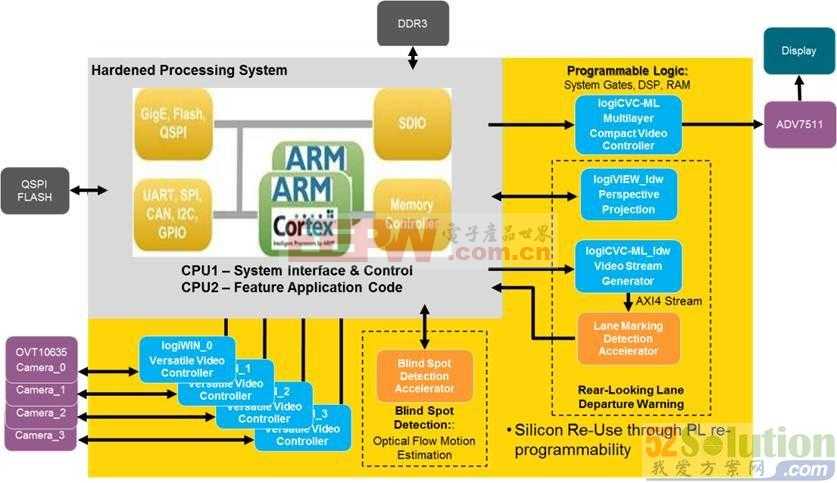

探索ZynqSoC如何实现串口与DDR的有效整合之前,需先深度了解其内部构造。Zynq由处理单元(PS)与可编程逻辑(PL)两个部分构成。PS部分包括双核ARMCortex-A9处理器、各类外设接口及存储控制器等;PL部分则基于XilinxFPGA架构,具备高度灵活的硬件加速与定制化能力。借助串口与DDR的紧密配合,ZynqSoC得以充分发挥其双重优势,助力软硬件协同设计中的高效数据交互。

实践应用中,掌握ZynqPS部分设置串行通讯模式和由PL部分将数据写入DDR存储器的方法至关重要。需深刻理解Zynq内核总线结构及其寄存器对应关系以及时序调控技术。全面理解Zynq架构特性,方能有效完成串行读取与写入DDR的任务。

2.串口通信协议

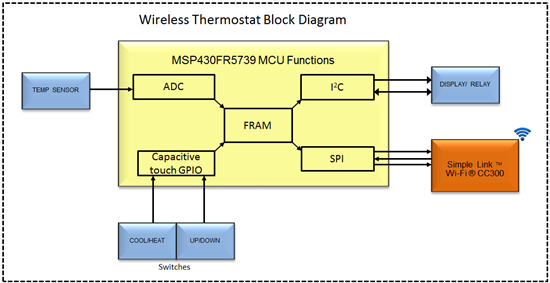

串行通信为实现设备间数据交互的主要手段之一,同样在Zynq与外界设备间进行信息互通时,各类串口协议则不可或缺。如通用异步收发器(UART)、同步外设接口(SPI)及现场总线成熟访问(I2C)等,各具特色且对工作模式和时序有严格规定。在挑选适宜的串口协议时,需综合考量数据传输速度、距离以及能耗等要素,并依据实际需求作出明智抉择。

针对Zynq串口读取DDR存储的操作,首选UART作为通信协议。UART具备简洁、稳定及经济实惠等优势,能有效地与DDR交换数据。只需对Zynq内嵌的UART模块进行配置,设定适当的波特率、数据位数和校验位等参数,便可实现高效率且可靠的串口通信,确保数据传输的精确性,从而提高整个系统的运行效能。

3.DDR存储器介绍

DDR(双倍数据速率)内存是电脑系统中的典型组件,具备高速度、大存储空间等特性,广受各类应用领域所青睐。依据不同世代划分,DDR存储器可细划为DDR1、DDR2、DDR3、DDR4等多个品种,每种都有特有的工作频率与时序规定。

在Zynq设备上从串口中向DDR存储器写入数据时,需深入理解内存地址映射以及速率适配的原则。为此,需精心设计内存地址空间的布置方案,同时依据实际运用需求挑选最适宜的DDR存储器型号与容量。以此可实现数据操作的高效率及优良性能。

4.串口读取数据到DDR

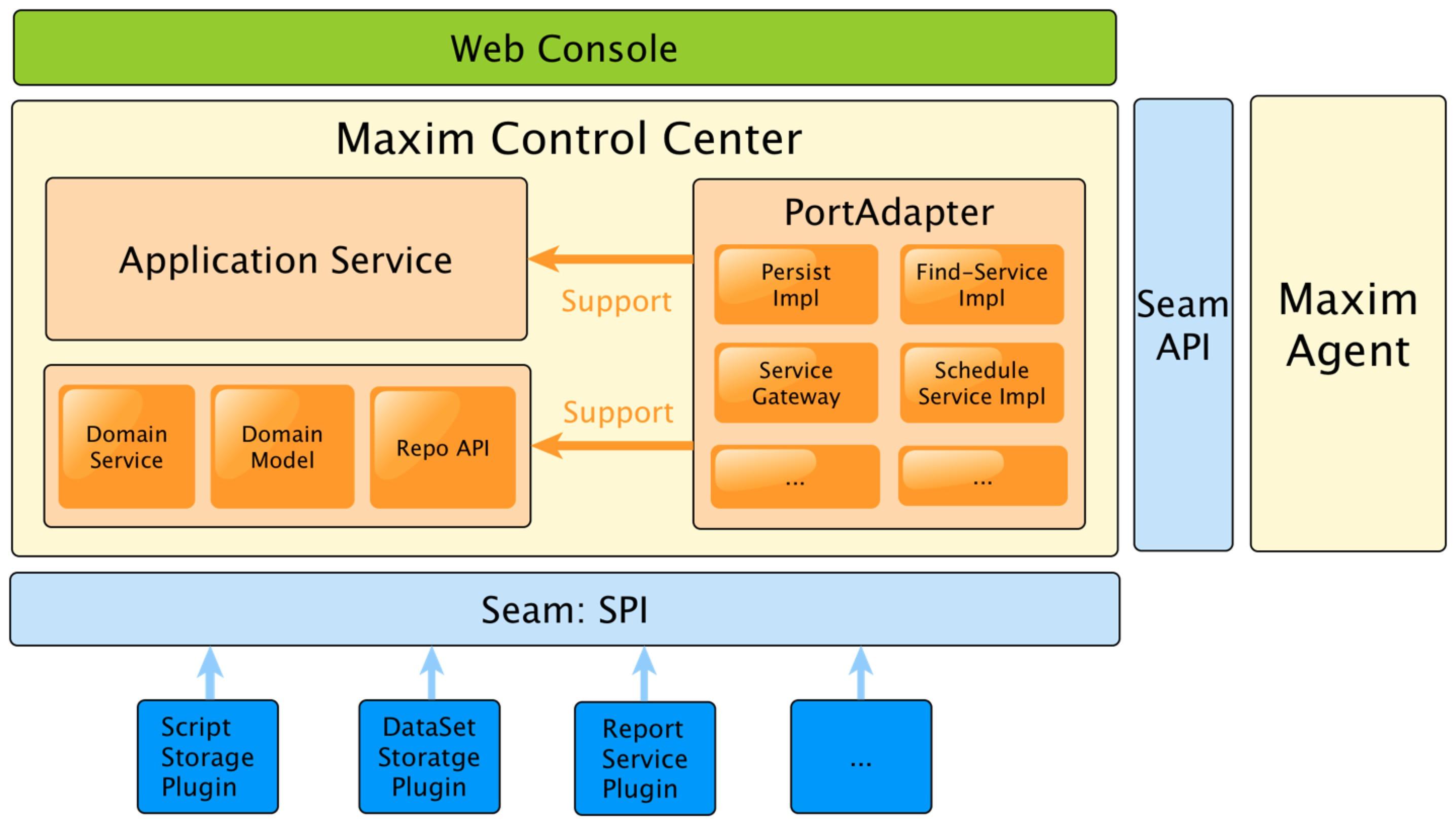

实战操作中,首要任务是对Zynq内部UART模块进行配置,设定相应参数,保障与外界设备的顺利通讯。接收来自外设的信息后,数据可借助DMA(直接内存存取)引擎直接传输至DDR存储空间,从而减轻处理器压力,提高数据传输速率。

针对DMA引擎的数据传输作业,需妥善管理其缓存区并完善相应中断处理机制,以保证数据能准确无误地传输至目的地。同时,为应对各种规模与速率的数据传输需求,有必要适时调整DMA引擎的相关参数,以实现最优性能表现。

5.从DDR向外部设备发送数据

除从外部读取数据至DDR外,还能将DDR内数据传输至外部设备处理或展现。此过程需利用DMA引擎将DDR特定地址处数据载入缓冲器后,再经由UART模块传递给外部设备。

在发送流程中,务必考虑DMA引擎设定及缓冲区容量调节等要素,针对接收终端特性进行速率调整等操作,以实现数据稳定可靠的传输。运用多样化DMA引擎运作模式与触发机制,满足各类外设的不同需求。

6.异常处理与性能优化

针对常见的异常情况如超时或数据包丢失等,在制定串口读写DDR解决方案时应着重关注其相应的应对策略。比如,采用重发机制及误差检查码校验等技术,以提升系统的稳定性与容错能力。

在实施串口读写过程中,应重视性能的优化。例如,通过精心规划DMA引擎运行模式以减轻CPU负担;采纳多层次缓存结构以提高数据传输速率;以及精细调整内存地址映射方式以缩短访问延时而提高整个系统效能。

7.应用案例与展望

在此要着重强调的是,我们能够在工业自动化、物联网以及人工智能等多个领域中找到Zynq串口与DDR技术的融合实例。例如,在智能监控系统中的应用中,Zynq凭借其强大功能实现了视频流的实时采集和存储于DDR之中;而在家居智能化方面,串口则与各类传感器紧密配合,将所收集的环境信息保存在内存中。

在科技日新月异及市场需求持续增长的背景下,Zynq串口读写DDR技术展现出巨大的潜力,必将迎来更为辽阔的发展空间。对于更深层次的技术开发以及新的应用场景的创新探索,我们充满信心与期待。