身为一位致力于芯片设计领域的工程师,我对于DDR接口FFE设计方法的深入研究一直是工作中的重心所在。DDR接口即是所谓的双倍数据率接口,这是目前在芯片设计领域日益广泛使用的一种标准接口方式,其主要目的在于提升数据传输速度与效率。至于FFE(前馈均衡器),它是一种被广泛应用的信号处理技术,用以补偿信号在传输过程中所产生的衰减及失真现象。本篇文章将对DDR接口FFE设计方法进行全面剖析,从理论层面到实际操作,分享我个人的经验与见解。

DDR接口概述

让我们首先探讨DDR接口的基础知识。该接口为双边缘时钟传输结构,较传统单边缘时钟SDR接口而言,其能在同一时刻输送两倍的数据量,大幅提升了数据传输效率。因此,在当代的芯片设计领域,DDR接口已广泛运用于处理器、存储设备以及通信芯片等方面,成为保障系统高效运行的重要因素之一。

DDR接口的设计涵盖了时序控制、电路匹配及信号完整性的多重环节,而时序控制乃关键所在。设计过程中需关注信号间时序关联,确保数据稳定传送。同时,为提升信号传输品质,FFE技术已被广泛应用于DDR接口设计之中。

DDR接口设计流程

在实战中的DDR接口设计,需遵循严谨且系统化的流程,涵盖了需求解析、电路设计、仿真校验以及布局布线等关键要素。最初阶段,工程师须深度剖析DDR接口的具体需求,包含数据传输速率,时序规制,能耗限制等方面。依据以上需求,展开相应的电路设计工作,挑选合适的电路结构与信号处理算法。

电路设计完毕后,需运用仿真技术对此款DDR接口进行性能分析及验证,主要涉及信号完备性及时序稳定性两大指标的审核,以确保其状态达到预期设定。若有必要,可进一步实施板级仿真,来确认此接口在此类实际PCB板中的运行状况。

FFE技术在DDR接口设计中的应用

在DDR接口设计领域,FFE技术作为关键信号处理手段,具有不可忽视的重要性。借助于发送端所加的预编码电路以及接收端所设的均衡器电路,可有效抵消信号传输过程中的衰减与失真现象,从而提升信号传输品质。在此基础上,精心设计并优化FFE电路,将有助于进一步增强系统的抗干扰性及稳定性。

在DDR接口设计过程中,针对各种信号特性及需求,我们会运用线性均衡器以及决策反馈均衡器等多种FFE电路形式进行设计,以此保证最佳的信号传输性能。此外,在实际操作中,我们也需深入了解并合理控制均衡器的调解范围、功耗及占空比等因素,进而全面优化DDR接口设计,实现高效实用的产品功能。

DDR接口设计中的关键技术挑战

在DDR接口研发阶段,工程师常需应对诸多技术难题。首要问题即为时序控制,由于接口对时序把控要求极高,务必确保数据精准传送,故此环节至关重要。其次,信号完整性亦是挑战所在,鉴于DDR接口在高速数据传输过程中易受信号衰减及串扰等因素干扰,故需借助信号完整性分析与优化以保障数据传输之可靠性。

此外,功率消耗与面积大小亦为DDR接口设计时必须考量之关键要素。随着芯片整合度日益提升及能耗需求持续上涨,工程师们在确保性能的基础上,需尽可能降低能耗并缩小面积,因此对DDR接口设计的挑战愈发严峻。

未来DDR接口设计的发展趋势

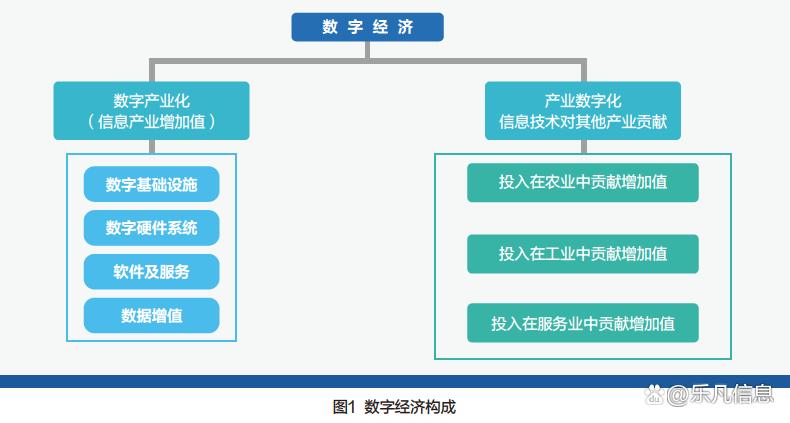

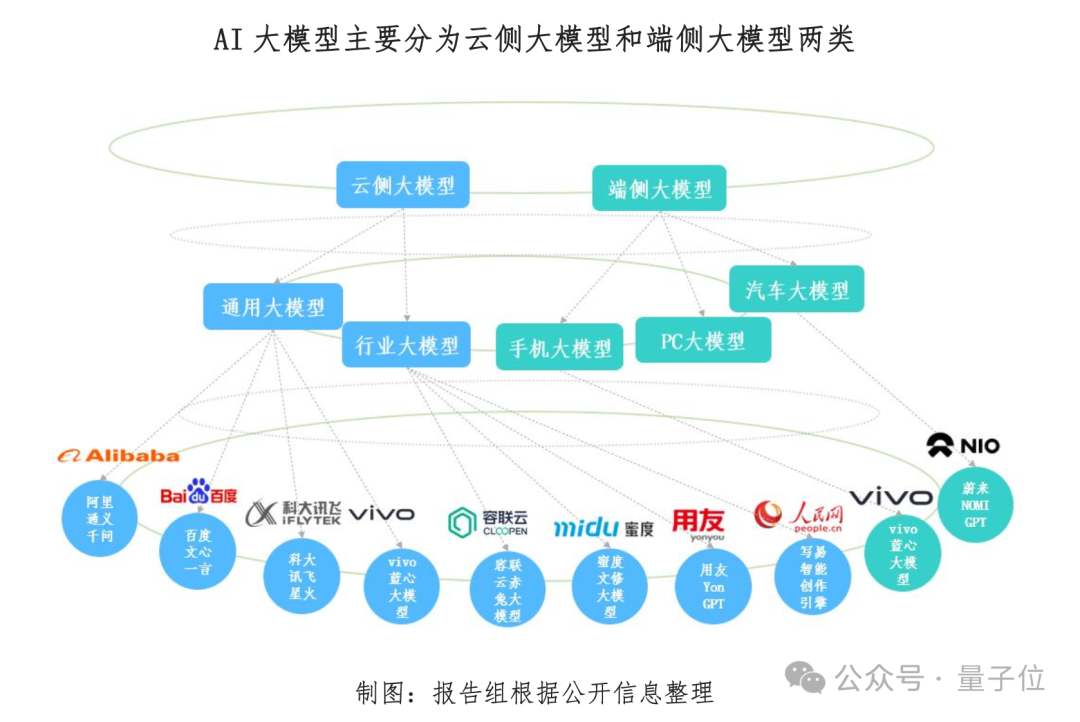

伴随着通讯科技与芯片设计的持续进步,DDR接口设计正逐步完善升级。展望未来,DDR接口设计将进一步重视高速信号传输的稳定可靠,运用先进的信号处理算法及设计技术,以满足日益增长的数据传输需求。

此外,得益于AI和IoT技术的飞速进步,DDR接口已成为高性能计算及云计算应用中的核心环节。展望未来,DDR接口设计将进一步强化与其他芯片模块间的协同作用,以提升整体系统效率。

总结

在当今芯片设计领域中,DDR接口的FFE设计策略尤为关键,其内容涵盖了时序控制、信号完整性以及功耗优化等多重维度。借助FFE技术的恰当运用,可显著提高DDR接口传输品质与稳定程度,从而为系统性能的提升奠定坚实基础。展望未来,DDR接口设计将持续向高速化、低功耗化及高可靠性方向迈进,为数字化社会的繁荣进步贡献力量。