身为计算机专家,我日复一日地与各类硬件打交道,其中DDR3内存便是频繁出现在任务中的重要部件。DDR3内存作为一种主流的电脑存储器,拥有卓越的性能及稳定性,深谙其读取写入的规范,对提升系统效能尤为关键。内存的读写规则关乎数据储存、获取与传输等各个环节,这正是我们需要深度解析的重点所在。

在探究DDR3内存读写规定之前,必须理解其基础构造及运作机制。DDR3内存借助内存控制器与处理器进行信息交换,实现数据的读取与写入。内存控制器负责协调各内存模组间的数据传输,而DDR3内存的读写规定则决定了数据在内存模组中的存储与访问方式。

DDR3读操作

DDR3内存的读操作,即为处理器从内存中获取数据的过程。这一过程需先行将所需读取数据的地址传送给内存控制器,再由内存控制器根据此地址搜寻并取得对应的存储单元中的数据,并将之传输至处理器中。为了确保数据准确无误地被检索及传输,DDR3存储器读操作中的预充电和CAS延迟等环节均遵循特定规则。

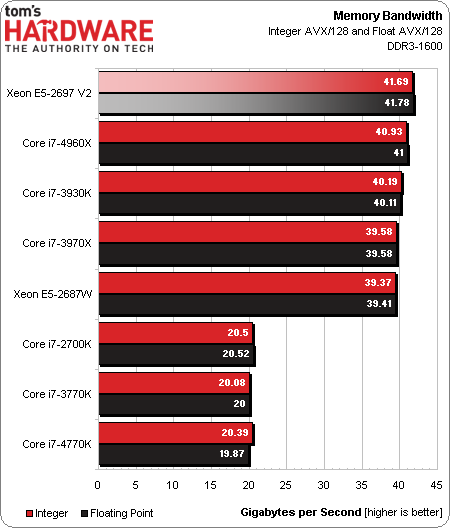

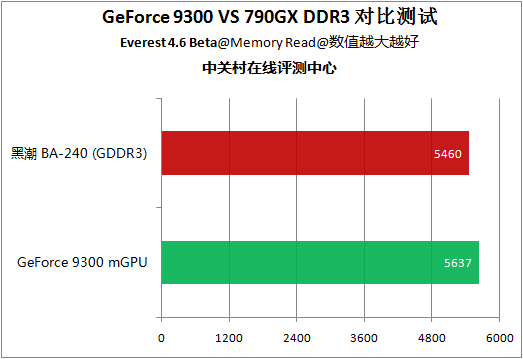

在执行DDR3内存的读取操作过程中,必须充分考虑其时序与时钟频率两个关键参数。时序即为内存模块内部各信号的传输次序及其之间的时间关联;而时钟频率则直接影响着数据传输的速率。深入理解并合理运用DDR3内存的时序与时钟频率,能显著优化内存读取操作,进而全面提升系统性能表现。

DDR3写操作

除读操作为主外,DDR3内存的写操作亦为系统运作中的重要组成。写操作即处理器将数据写入内存之进程,由内存控制器将其准确传输至特定存储器单元。在DDR3内存执行写操作时,需遵守一系列规定,如数据写入地址及数据传输时序等。

针对DDR3内存的写入功能,必须保证数据稳定且精确无误地输入至目标存储位置,防止数据遗失或产生误码。理解DDR3内存的写入原则,对维护数据完整性具有决定性的影响。

DDR3读写规则的优化

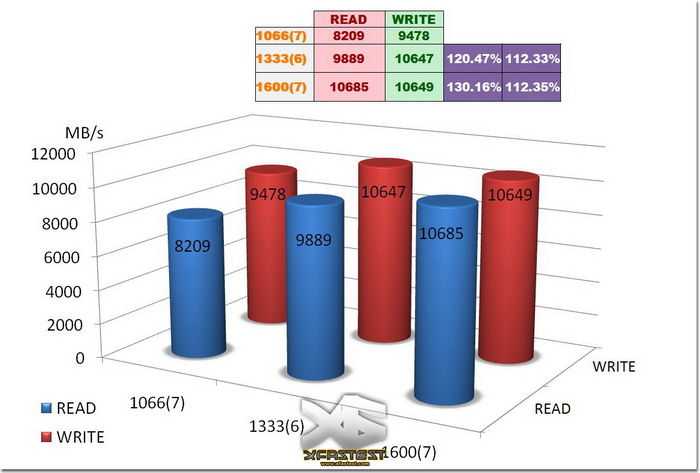

为优化DDR3内存性能,可从多个角度展开。首先,对时序与时钟频率进行精细调节,以提升数据传输速率及系统反应速度。其次,合理规划内存读写操作次序,规避读写冲突与数据竞争,从而增强系统并发能力。

另一方面,有效提高DDR3内存读写性能的方法包括扩大存储模块容量,增强传输带宽,添加更多内存通道等。以科学搭配系统硬件以及完善的读写策略为基础,我们有可能挖掘并发挥DDR3内存的强大能力,从而提高整个系统运行的生产力。

总结与展望

在深度剖析DDR3内存读写规则后,我对此项技术有了更为透彻的认识。DDR3内存是计算机系统中的关键组成部分,其读写规则对系统性能及稳定性有着深远影响。掌握和优化DDR3内存的读写规范,有利于全面提高系统性能,进一步优化用户体验。

随着科技日益精湛与硬件推陈出新,未来DDR3内存的读写规则有望得到更优改善,从而为计算机系统的高效运作提供有力支撑。期望通过持续学习与实践,能在此领域取得突破性进展,为技术创新及应用贡献更多力量。