身为电子工程师,我对DDR(双倍数据传输率)型差分时钟充满了研究热情。这类时钟在数字电路中起着关键性作用,尤其是在DDR接口设计领域。本文旨在深入剖析DDR差分时钟的类别、特性及其实际运用,期望为广大读者提供有益参考。

1.什么是DDR差分时钟?

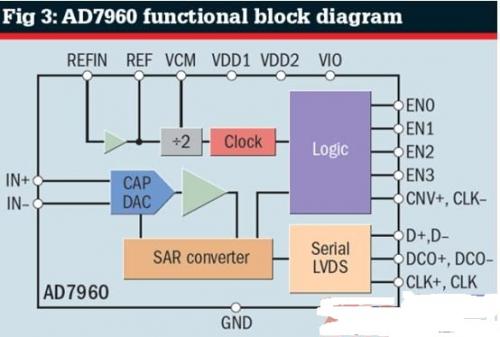

欲深入探索DDR差分时钟类型,需先明晰何谓DDR差分时钟。此乃专为双数据速率接口设计,运用差分信号传输技术实现更高数据速度与更强抗干扰力之钟号。DDR差分时钟主要由时钟正向信号(CLKP)及时钟反向信号(CLKN)构成,其差分电压可显著降低信号传输过程中之噪声干扰。

精准与稳定的时钟信号对DDR接口数据传输起着决定性作用。采用差分时钟设计可显著提升时钟质量,确保高速传输中数据精确且无误地送达指定地点。

2.DDR差分时钟类型有哪些?

在实践中的电路设计环节,DDR差分时钟务求有LVDS(低压差分信号)、HCSL(高速差分信号逻辑)及LVPECL(低压正/负电源区别分信号)等多种选择。各类别差分时钟各有所长,如电平、能耗以及传输速度等方面均有其独特之处与适用领域。

-LVDS技术:其以低能耗、低压差分信号传输闻名,常用于DDR接口设计之中。LVDS差异性时钟的特点在于低能耗与强大的抗干扰能力,极其适合高速度数据传输环境。

-HCSL:高速差分信号逻辑具备优异的数据传输速度与低时钟抖动优势,尤其适用于特别强调时间同步的应用环境。

-LVPECL:作为一种低电压正负向差分信令,具备较强的输出振幅及高速传输性能。因此,LVPECL差分时钟常用于对信号振幅有严格要求的应用环境。

3.DDR差分时钟类型的选择

紧扣实际电路设计需求,选定适当的DDR差分时钟类型显得尤为关键。实际应用环境需选用多元化的差分时钟以确保系统的运行效能与稳定性。当涉及到DDR差分时钟的挑选时,应着重关注以下几点:

-传输速率:依照系统需,确定预期值,进而认定合适的差分时钟型态。

-电平要求:各式差分时钟需依据系统电平需求进行选型,因其电气特性各异。

-能耗考量:各种差分时间在能量消耗上各有差异,故需根据系统能量预算挑选适用类型。

需全面考量众多要素后,方能选出最适合的DDR差分时钟模式,以保证系统高效稳定运转。

4.DDR差分时钟类型的应用

DDR差分时钟在数字电子电路设计领域应用广泛,尤其是在高速数据传输环节。比如,在存储器控制设备、快速接口以及通讯网络等方面,均离不开DDR差分时钟以保证数据传输的稳定性与可靠性。

高速数字信号处理系统中的DDR差分时钟选型,决定了系统的性能与稳定。合适的差分时钟能够提升数据传输速度,降低能耗及时钟抖动,从而全面提升系统效能。

5.DDR差分时钟类型的发展趋势

伴随着数字电路设计的持续革新与优化,DDR差分时钟亦在逐步演变和精进之中。展望未来,DDR差分时钟有望实现更快的传输速度、更低的能耗以及更强的抗干扰性能等优势。

伴随着5G及物联网等新技术的飞速进步,DDR差分时钟型别的需求必将日益增长。预计未来DDR时钟将呈现出多元化及专业化的特色,以满足各行各业的独特需求。

6.总结

深入研究和剖析DDR差分时钟类型使我深感时钟信号在电子工程中的关键性。选择适当的DDR差分时钟类型对于系统的高性能与稳定运行具有决定性作用,需全面权衡各有利弊作到理性抉择。

本文旨在让读者对DDR差分时钟有更深层次认识,引导其在实际电路设计过程中作出正确决策以提高系统性能与可靠性。