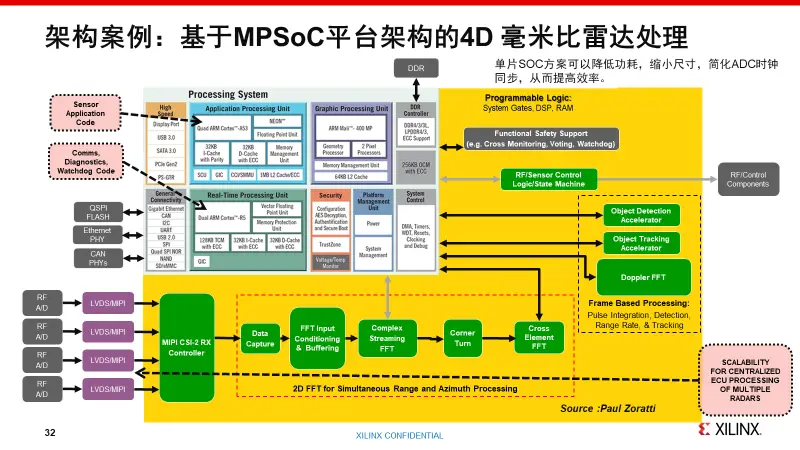

身为心醉于FPGA技术的工程师,我长久以来对其DDR缓存深度产生浓厚兴趣。这一参数对于FPGA设计极具重要性,直接影响着系统效能及稳定运转,同时也是影响功耗消耗以及数据丢失和冲突预防的关键因素。出于这点,我决定对FPGADDR缓存深度展开深度研究,揭示其深层次奥秘。

1.DDR缓存深度的概念

在深入探讨之前,有必要先明确何谓DDR缓冲器深度。简而言之,它代表芯片内部DDR存储器容纳数据的能力。在设计过程中,我们会利用FPGA中的DDR存储器来存储大量数据,比如图片、视频以及音频等等。因此,设定合适的DDR缓冲器深度尤为关键,因为它直接影响着FPGA同时缓存的数据块数量,也就关系到整个系统的数据处理速度和吞吐量。

在实践操作中,适度设定DDR高速缓冲存储器的深度能均衡系统的运算速率和资源消耗。若此深度过浅,不容忽视的问题便是会引起读写速度迟滞,进而对整个系统的效能产生负面效应;反之,倘其深度过大,则易造成FPGA内硬件资源的无谓损耗,从而削弱了系统的机动性。因此,设定DDR高速缓冲存储器的深度这一环节需要我们依据系统实际需求以及硬件配置进行审慎考量。

2.影响DDR缓存深度的因素

在考虑DDR缓存深度设定时,需考虑多项要素。如处理数据所需延迟的需求,不同时期的应用程序对此敏感度不同,从而决定了DDR缓存深度的选择。再者为处理数据所需吞吐量的维度考量。若有些应用有更高的吞吐量需求,那么适度提高DDR缓存深度就能提升数据处理的效益。

在此关键结构中,系统硬件资源对DDR缓存深度产生深远影响。由于FPGA内部资源的限定性,过深的DDR缓存不但可能造成资源的无谓消耗,还可能干扰其他功能模块的正常发挥。故而,在设定DDR缓存深度时,应审慎权衡总体系统性能与资源占用状况,从而找到理想的平衡点。

3.DDR缓存深度的优化策略

依照具体应用环境,为DDR缓存深度配置适宜优化策略。首要原则为依据数据处理现实需求,以保障系统的即时性及稳定性得到充分满足。同时,匹配FPGA内部资源使用状况,精心设定DDR缓存深度,规避资源浪费,全面提升系统性能。

此外,可实施动态调整DDR缓存深度策略,依据系统运行期间的数据处理状况进行调整,从而实现最优性能与资源利用效率。此策略能在系统运行期间持续优化DDR缓存深度,满足各类数据处理情境需求,提升系统灵活性及适应力。

4.DDR缓存深度的实际案例

于此实际项目中,曾面临DDR缓存深度的问题。为应对对高速数据处理的需求,需深入优化DDR缓存以提升处理效能。经过多番调试与优化,最终决定采取动态调整DDR缓存深度策略,即依据系统运行实况调整深度,测试显示结果显著。

经历此案,深切感受到DDR缓存在FPGA设计中的关键性,以及其设定对系统性能的影响程度。未来工作中,我将更专注于探索DDR缓存深度的高效策略,以期持续提升系统的数据处理效能与稳定性。