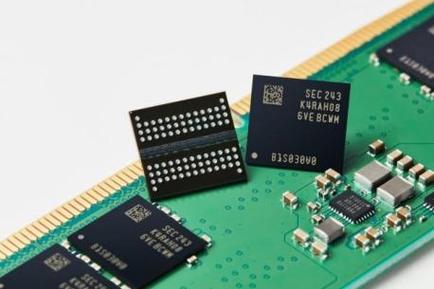

初涉DDR4时序调整之理时,我对此全然不解。然而,通过深入学习与实践,我逐步领悟到了DDR4的精髓。作为第四代双倍数据速率同步动态随机存取存储器,DDR4是高速存储的新标杆,其带宽及时序性能较DDR3均大幅提高。探索DDR4背后的机理,对于揭示其时序调节法则具有深远意义。

DDR4中时序规律主要指内存各信号间的时序关系,包括时钟周期及延迟时间等。而调整时序规律即依据内存模块特性,科学设定这些参数,实现最高效与稳定运行。这就需要深入掌握DDR4内部构造,并通过反复调试与实验找寻最优时序设置。

理论知识与实践经验相结合

在深度研究DDR4时序规律中,理论与实践缺一不可。理论认知有助于深化我们对于DDR4内在架构及运作机制的理解;而实际操作经验则可校验理论之准确性,进一步揭示时序调整规则的核心奥义。

实践过程中,我发现了一些调节时序的普遍性原则。第一,各个时序参数彼此关联,应作为一个整体来考虑。第二,不同的硬件设备会对时序设置产生特定需求,必须针对实际情况作出相应调整。第三,稳定与性能之间往往难以两全其美,有时候需要权衡利弊。第四,为寻得最优时序设定,需经过不断测试和调整,这其中需要我们保持足够的耐心和细致。

时序参数的调整与优化

实战经验告诉我们,DDR4时序参数的精细调节颇具挑战性且精细入微。首当其冲的便是CAS延迟(CL)参数,这代表了列地址选通至数据读/写输出所需的等待周期,亦是衡量内存访问效率的关键要素。理想状况下,适度缩小CAS延迟可显著提升内存效能,然而同时也可能加剧内存控制器的负荷,需要寻求性能与稳定间的最佳平衡。

接下来是RAS预充时间(tRAS),即数据行关闭前需要预充的时长。该项设定对内存延迟与稳定运作具有重要影响,适当地调整能提升内存读写速率及整体效能。此外,包括写入时序参数(tWR、tWTR等)在内的其他参数亦需依据实际需求进行微调,确保内存正常运行并保障数据稳定性。

内存频率与时序规律的关系

DDR4内存模块的频率代表其单位时间内的运行速度,常以MHz为单位衡量。内存频率与时序规制间紧密关联,频率的提升将对时序设定产生影响,需依据具体情况进行调整。通常而言,提高内存频率可增强内存带宽及整体性能,然而同时也会加大时序参数的需求,需更为精准地进行调节方能实现最佳效果。

另外,提高内存频率同样也会对系统的稳定性产生影响,过快的速度可能使得内存控制器难以适应,引发崩溃现象。因此,在更改内存频率设定时,务必小心行事,逐步提高频率并进行稳定性检测,保证系统的持久运行。

温故知新,持续学习与实践

探讨DDR4时序调整的关键环节中,我深感知识和实践二者之于成功的重要性与不可或缺性。在积极汲取新知的同时,我也注重对旧知的温习与掌握。这不仅助我拓宽眼界,也使自身技艺水平得以提高。实际操作中,我致力于发掘并解决问题,从而更深入地洞察到DDR4内存运作机制以及时序调整原则的内涵。

持续的学与践赋予我对DDR4调序规则的深入理解。唯有持续掌握新知,实践并积累经验,方能在此领域不断提升,揭示新的规则。DDR4虽繁杂,但凭借热情与毅力,便可驾驭之,收获喜悦及成就。