每片内存颗粒都存储着大量信息,作为资深硬件工程师,我深感理解DDR内存控制器地址映射之难。它不仅关乎技术,更是对数据流畅传输的一种艺术把控。在此,我愿与您共同探讨DDR内存控制器地址映射的奥妙之处。

地址映射的基础概念

地址映射是内存控制器中至关重要的环节,其将处理器与内存紧密相连,确保每个指令能准确地寻址并写入内存指定位置。尽管这一过程看似简单,但其中却蕴含着诸多复杂因素。例如,内存地址的生成需精确至每一位,任何微小的误差均有可能引发数据丢失甚至系统崩溃。

地址映射不仅关乎技术难题,更要求深入理解内存布局。各内存模块均具独特物理构造,需借助控制器将物理地址个性化转为逻辑地址。在这个转化过程中,追求高效精确的地址映射显得尤为关键,直接影响着系统稳定性与性能表现。

DDR控制器的设计考量

为了设计出一款高效的DDR控制器,地址映射策略至关重要。需通过相应算法优化,降低延迟,提升数据传输速度。此外,该控制器还应具备高度灵活性,适配各类内存条及各种工作负荷。

实践设计过程中,诸多挑战纷至沓来。如确保数据完整性与提升内存使用率相匹配;实现不同内存模式间的高效切换等,这些问题的解答都潜藏于繁复的地址映射逻辑之中。每次改进,既是对控制器性能的提升,亦是对工程师技术实力的检验。

地址映射与内存带宽的优化

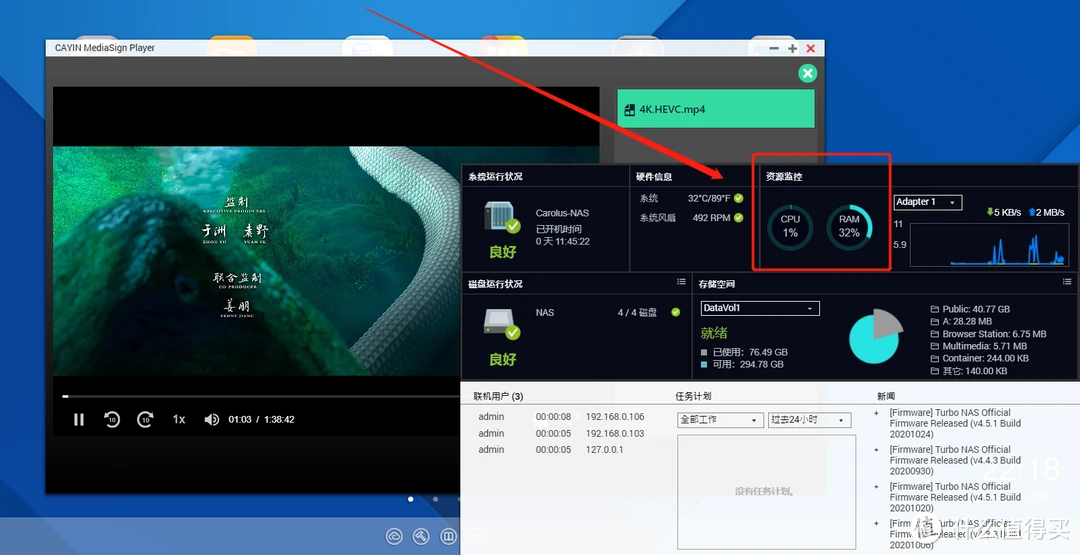

内存带宽直接影响着系统运行效能。优良的地址映射策略对其有积极影响,可显著提升整体系统效率。因此,在控制器设计阶段,应充分考虑内存访问模式及运用巧妙的地址映射方法以优化这些模式。

通过对内存访问模式的预测,控制器能够预先填充所需数据,降低等待时长;同时,借助动态调整地址映射的策略,适应实时的工作负荷,优化内存访问路径。尽管此类设计方案可能繁琐,却能显著提高系统效率。

处理多核处理器与内存控制器的协同

随着多核心处理器应用范围扩大,内存控制器面临着日益增长的压力,因需满足同时存取内存的需求,这需要控制器具备高效的地址映射管理和防止冲突能力。因此,除了对高性能的需求外,优秀的并发控制机制也显得尤为重要。

在多核系统环境下,地址映射策略面临更为复杂的挑战。不仅要解决各核心间的通信难题,还需解决如何利用地址映射进行有效协调的问题。此举不仅关乎技术层面,更挑战着系统设计思维。每个决策皆会影响到系统整体性能及稳定性。

实时的地址映射动态调整

实践中的工作负载呈现出显著的动态特性,这便要求DDR控制器具备相应的功能,实时调整地址映射策略来适应这种动态变化。这种动态自适应能力反映了控制器智能程度的高低。

为了实现实时调节功能,控制器需具备卓越的分析与决策能力。这包括实时监测内存利用状况,解析访问模式,并根据这些信息调整地址映射策略。尽管如此会使控制器更为复杂,然而正是此类能力的提高,才使得整个系统更具灵活性及适应力。

未来的发展趋势与挑战

随着科技创新推动,DDR内存控制器的地址映射技术正在飞速进步。展望未来,更智能的控制器将具有更出色的内存预知与管控能力。然而,伴随着新兴内存技术的涌现,地址映射策略正面临前所未有的挑战。

新型非易失性内存(NVM)的崛起,正在颠覆传统内存应用模式。因此,设备控制系统需适应这种新型内存技术,适时调整地址映射策略。尽管面临巨大挑战,但这亦为工程创新带来新契机。

结尾:

本篇文章深度探讨了DDR内存控制器地址映射的各个方面。涉及基础理论至设计原理、带宽调优到多核协作、动态调整乃至将来的课题,每一步骤无不体现出我丰富的技术储备与勇于探索的精神。身为硬件工程师,能涉足于此领域实感荣耀。最后,我期待您也投身于这个充满魅力的技术世界。欢迎交流,分享见解,共同拓展这个神秘且富有魅力的研究领域!