面对信息化加速发展的今天,深入解读DQSB与DDR这两大电子领域核心概念间的紧密关联,对内存控制器设计的全面把握及优化具有深远意义。本篇文章着重解析二者间的内在联系及其在内存系统中的关键角色和影响力。

1.DQSBUF与DDR的基本概念

接下来,首要任务是理解DQSBUF与DDR的基础定义。前者为承载并增强数据时钟信号的缓冲器,其主要功能是保持DDRSDRAM控制器内数据的稳定传送。至于DDR,即双倍速率数据存储器(DoubleDataRate),凭借其能在每个时钟周期传输两倍数据量的能力,大幅提升数据传输效率。

DQSBUF主要负责接收时钟信号并对其进行放大,随后传递至内存控制器,以便保证数据传输稳定性;DDR内存则借助于提升高低电平两个边缘的数据传输速度,实现了更高的传输效率,进而提升整个系统的性能表现。

2.DQSBUF的工作原理

DQSBUF功能的实现主要由三个模块组成:输入缓冲、时钟放大以及输出缓冲。首先,输入缓冲模块从外部获取时钟信号进行稳态处理;然后,时钟放大器进一步提高信号强度;最后,输出缓冲传输经过加强的信号至内存控制器完成数据传输过程。

为确保高性能与稳固性,对于精准的设计效能及布局安排提出严谨要求。在前置直接序列缓冲器(DQSBUF)的设定中,DDRSDRAM控制器的运行状态和性能表现深受其影响。因此,理解并优化此类缓冲器显得尤为关键。

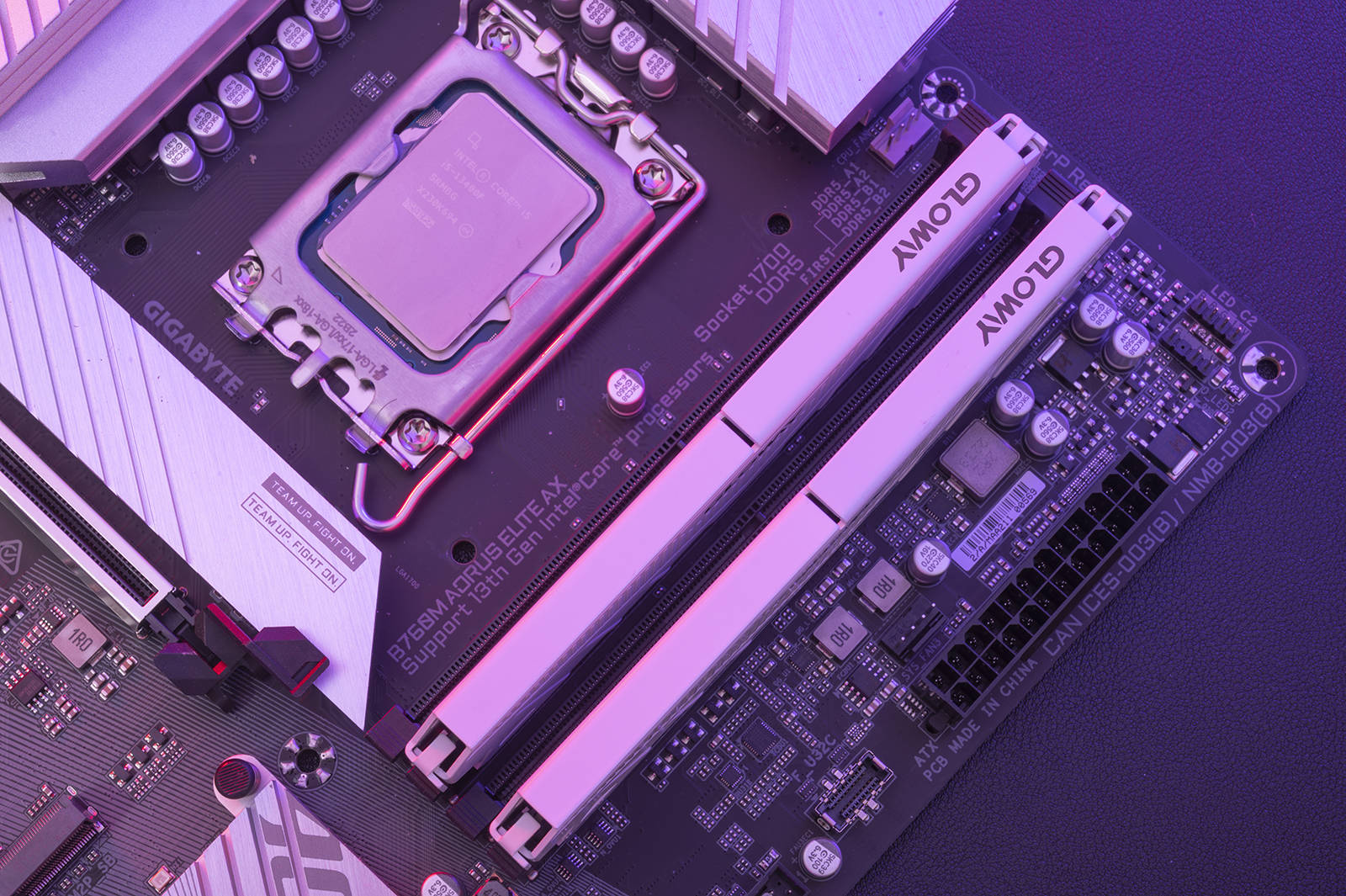

3.DDR内存控制器的设计

在当今电脑系统中,DDR内存控制器作为关键部分,肩负着对内存进行有效读写控制及管理的重任。其设计涵盖了许多技术难点,如时序控制、信号处理以及数据传输等多个类别。其中,如何精准地设计并削减DQSBUF也成为了决定性因素。

DDR内存控制器研制过程中,需着重考量时钟信号稳定性、数据传输效率及能耗管理等关键环节。针对这一需求,DQSBUF应运而生,其设计需均衡兼顾以上诸多因素,以确保整个内存系统运行稳定并展现出色性能。

4.DQSBUF与DDR的关系

DQSBUF与DDR间关系密切,两者协同作用,决定了内存系统的整体表现及稳定性。在DDRSDRAM控制器中,DQSBUF主要承担数据时钟信号的接收与放大功能;而DDR内存则是通过每周期传输双倍数据量以提升传输效率。

总所周知,DQSBUF的设计及优化直接决定了DDR内存的读写表现以及稳健性。优秀的DQSBUF能有效确保时钟信号的精确传递,从而提升内存体系的性能与信赖度。为此,DDR内存控制器的设计需深度考量DQSBUF的特性并进行相应的优化处理。

5.DQSBUF与DDR的优化策略

关于对DQSBUF和DDR的深度优化,需从电路架构设计,布局优化,及信号完整性的角度全面考量。首先,调整合理的电路构造和参数,可提升DQSBUF的运行性能和稳定性;其次,依据科学的布局方案和信号线路规整,有助减小信号传输延时、降低能耗。

通过运用时序调整及信号匹配技术,DQSBuf与DDR间的匹配得以优化,从而提升了内存系统的运行效率与稳定度。综合运用以上策略,便可确保两者实现优异匹配,进而提升内存系统的整体性能表现。

6.实际应用与案例分析

实践操作中,对DQSBUF及DDR的精细调整,对于提升系统性能和稳定表现至关重要。例如,数据中心服务器中,通过优化DQSBUF与DDR的搭配使用,不仅能够有效提升内存读写速度与数据传输效能,还能整体上增强数据中心的运算力。

除此之外,在嵌入式系统和移动设备领域,对DQSBUF及DDR进行深度优化亦能显著提升性能。经过精心设计和调整,有望实现低功耗运行,进一步延长电池使用寿命,进而提升设备的用户满意度。

7.总结与展望

总结论点,DQSBUF同DDR可谓是息息相关,共同决定了内存系统的效能与稳定性。在内存控制器的精心设置与精益求精过程中,务必重视调整DQSBUF与DDR间的和谐共处,方能达到系统性能的最大化。展望未来,伴随电子科技日新月异的进步,如何优化DQSBUF同DDR将成为内存系统设计的重点课题。

在实践之中,我们需不懈探究并创新,以打造出更具效益且稳定的DQSBUF及DDR优化策略,以应对日益增长的计算需求和多样化的应用环境。团结协作,我们有信心进一步提高内存系统的性能和稳定性,为信息技术的持续进步提供助力。