随着芯片制造工艺的不断进步,单个芯片的晶体管数量持续增长,从数万级到今天的数百亿级。

长期以来,提高晶体管密度一直是实现更大规模集成电路的主要途径,我们的关注点也一直聚焦在芯片制程的升级上。

但随着工艺临近物理极限,这种路径已经难以为继,多芯片封装技术的出现了,给了我们另一种提升晶体管数量和电路规模的途径。

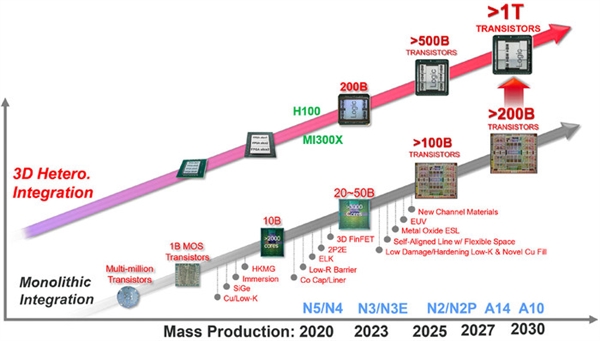

就像台积电最近在IEDM展示的芯片技术线路图那样,在这张线路图上有3D Hetero Integration和Monolithic Integration两种不同的芯片集成方式:

1、3D Hetero Integration,即异质3D集成技术。它是通过垂直堆叠和互连多个不同功能的裸芯片(Chiplet),实现芯片堆叠的一种封装与互连技术。其优点是可以混合匹配不同工艺节点的芯片,实现更高性能密度。

2、Monolithic Integration,即单体芯片一体化技术。它是在一块硅基板上,使用统一的制造工艺集成不同功能的电路元件,产出单个大规模的复杂芯片。其优点是信号传输更快,芯片之间没有互连瓶颈。

两者都是实现大规模集成电路的重要方式。3D Hetero Integration依赖封装技术,Monolithic Integratio则依赖制程技术,在两者共同作用下,台积电预计在2030年前后实现整合超过1万亿个晶体管的芯片解决方案,单体芯片的晶体管数量也在快速增长到2000亿级,工艺制程将来到1纳米。

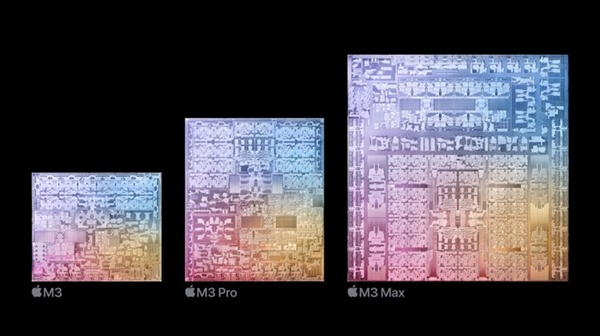

目前最大规模的单体芯片是苹果的M3 Max,这颗芯片中的晶体管数量达到920亿个,采用最先进的台积电3nm工艺制造。而在上一个工艺节点上(台积电4nm),最大的单体芯片是NVIDIA的H100 GPU,其核心集成有800亿个晶体管,芯片面积为814平方毫米。

至于多芯片集成方案,多见于AMD和英特尔的数据中心加速卡上,比如AMD今年推出的Instinct MI300X AI加速卡,借助台积电SoIC 3D片间堆叠和CoWoS先进封装技术,其内部集成了12个5/6nm工艺的小芯片(HMB和I/O为6nm),晶体管数量达到惊人的1530亿个。

而英特尔的Ponte Vecchio集成了47个FPGA和HPC加速器芯片,整套芯片包含了惊人的1000亿个晶体管。

在面向普通用户的产品中,AMD比Intel更早采用了多芯片封装技术。早在2017年发布的EPYC服务器处理器中,AMD就使用了多芯片模组(MCM)方案,在同一个处理器封装内集成了多个芯片级别的组件。

在2019年,该技术应用于Ryzen系列消费级处理器中,采用Zen2架构的AMD Ryzen 3000系列,首次使用晶片分离设计,其核心部分使用成本较高的台积电7nm,IO部分使用12nm,最后将核心和IO两个部分集成在同一块基板上。

随后,AMD持续优化了Chiplet架构,使AMD在性能和性价比上都占据明显优势,获得了巨大商业成功。

相比之下,Intel直到2024年底发布的酷睿Ultra处理器中,才在消费级产品上使用了多芯片集成封装技术,虽然比AMD的Ryzen系列稍晚,但这标志着x86芯片制造商全面进入多芯片时代。

酷睿Ultra具有Compute Tile、Graphics Tile、SoC Tile和I/O Tile四个小芯片,通过英特尔Foveros 3D封装技术连接到一起,在核心架构上实现了异构整合。

据Intel介绍,Foveros 3D封装技术的核心是通过微触点(Microbump)在逻辑芯片基板上垂直堆叠多个裸露芯片,并用TSV(通孔)实现芯片间的信号垂直互联。这种垂直3D封装方式可以实现异构芯片的混合封装和匹配,其空间效率和性能密度都很高,大大提升了芯片设计的灵活性。

毫无疑问,多芯片集成封装技术已经成为现在乃至未来五年芯片发展的重要技术,同时也让我们对过去封装技术的演进产生了兴趣。

芯片封装的发展历史和代表产品:

1、DIP封装:双列直插封装,1970-1980年代流行,典型产品为8086 CPU。

2、PGA封装:带连接孔的封装形式,因Intel 80486而流行。

3、PQFP封装:塑料四方扁平封装,应用于1990-2000年代的微处理器。

4、BGA封装:球栅阵列,以Pentium作为典型产品,90年代中后期流行。

5、Flip Chip CSP: 翻转芯片芯片级封装,应用于Intel Core和AMD Athlon系列CPU。

6、MCM封装:多芯片模块封装,EPYC服务器处理器。

7、Chiplet封装:面向现代处理器和AI加速器,如Zen 4和Intel Ponte Vecchio采用。

随着芯片的小型化和功能的增加,封装技术也在不断发展,以满足电性能和成本的需求。

这些多样的封装互连技术也必将不断演进与创新,推动产业实现更高性能与复杂度的异质融合芯片,以满足AI、高性能计算等应用的持续需求。制程与封装的协同发展,也将开启电子信息产业新的成长空间。