目前用上3nm工艺的只有苹果的A17 PRO芯片,并且随着台积电积极扩大3nm制程工艺的产能,代工龙头将在明年全面铺开N3E工艺,更先进的工艺在产能和成本上进一步取得突破。

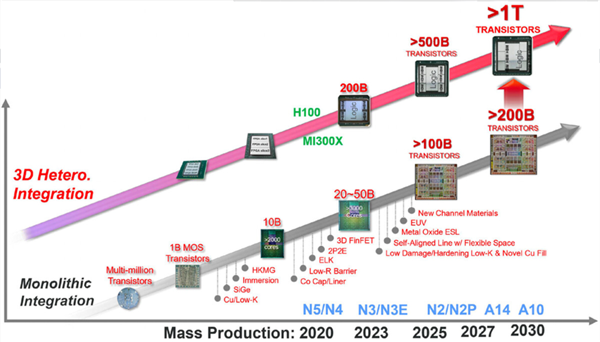

不过台积电的野心远不止于此,据外媒tomshardware报道,晶圆代工大厂台积电在IEDM大会上分享了其最新的Roadmap,计划在2030年推出1nm级的A10制程,实现单个芯片上集成200亿个晶体管,并依托于先进封装技术,实现单个封装上集成1万亿个晶体管的目标。

具体来说,根据台积电的计划,首先会在2025年量产2nm级的N2制程,2026年左右量产N2P制程,届时将会采用新的通道材料、EUV、金属氧化物ESL、自对齐线w/Flexible Space、低损伤/硬化Low-K&新型铜填充等技术。

将实现单颗芯片集成超过1000亿个晶体管,同时借助先进的3D封装技术,实现单个封装集成超过5000个晶体管。

在2027年之后,台积电还将量产1.4nm级的A14制程,2030年将量产1nm级的A10制程,实现单芯片集成超过2000亿个晶体管,借助3D封装技术,实现单个封装内集成超过1万亿个晶体管。

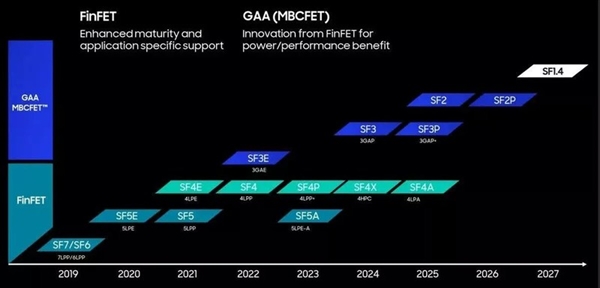

至于隔壁的三星,在去年实现第一代3nm制程工艺3nm GAA的量产,并且有消息称,三星将在2024年量产MBCFET架构的第二代3nm工艺3GAP,在原有的SF3E基础上做进一步的优化,之后还会有性能增强型的SF3P(3GAP+),更适合制造高性能芯片。

光有3nm还不够,三星希望能抢先一步台积电实现量产2nm,以速度压倒对方,从而在新一代制程节点上获得竞争优势。目前台积电和三星已经开始了2nm工艺的研发和竞争,双方都计划在2025年开始量产2nm工艺芯片。

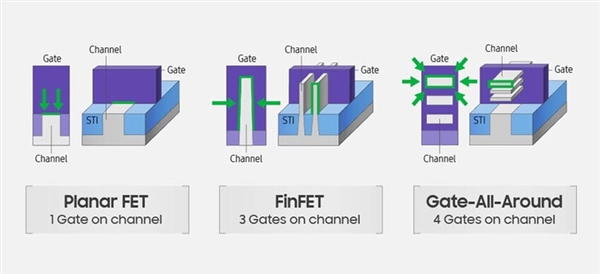

但是两家的工艺技术并不相同,台积电的2nm工艺将继续使用FinFET晶体管结构,但采用了新的Nanowire技术,可以进一步缩小晶体管的尺寸和间距。三星的2nm工艺将沿用GAA晶体管结构,但采用了新的MBCFET技术,可以提高晶体管的性能和稳定性。

总的来说,台积电的技术还是要优于三星的技术,至于国产芯片嘛,在制程上与国际差距还比较大,但在其他方面也有不少优势和潜力。我们还需要坚持研发,不断提升芯片的良率与工艺,才能不断缩短与国外先进技术的差距,甚至超越它们。