尊敬的读者,您好,我是电子领域的探索者小E,今日我们将探讨令广大工程师困扰不已的议题——DDR(双倍速随机存取内存)数据线阻抗匹配策略。虽然此项任务并非易事,但请放心,我将会运用最通俗的语言,引领您全面且深度地理解这项繁杂的技术难题。敬请各位网友跟随我的步伐,共同揭示DDR数据线阻抗匹配策略的谜团。

什么是阻抗匹配?

首先,了解何谓阻抗匹配至关重要。简而言之,阻抗匹配即能预防信号在传输过程中因阻抗不匹配所导致的能量损失过多。试想,倘若街道崎岖不平,那么您的奔跑是否将变得非常艰难呢?同理,当信号穿行于数据线时若遭遇阻抗不匹配,便如同在崎岖路面奔驰,大量信号能量因此损耗,传输效率自然降低。

阻抗匹配的价值无需赘言。良好的匹配能确保信号传输的稳健与高效率,特别是在高速数据传输等关键场景中,例如我们常接触到的DDR数据线。若未妥善实现阻抗匹配,可能引发数据误传、系统不稳定乃至完全崩溃。因此,优秀的电子工程师必须精通这项基本技术。

DDR数据线的特点

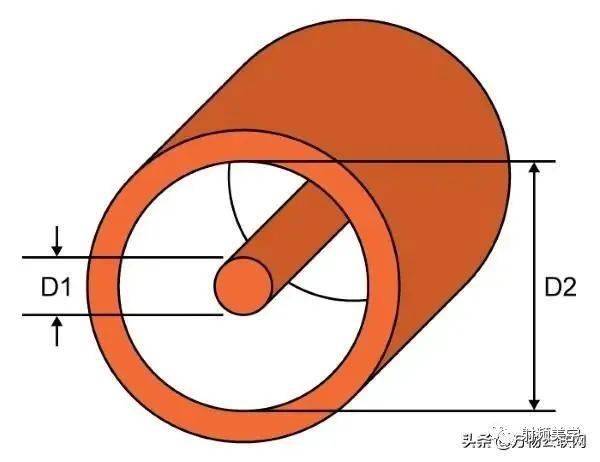

被简称为"双倍数据速率同步动态随机存储器数据总线"的DDR数据线,其基本功能是实现存储器与处理器之间的高速数据传递。这类数据总线由于需处理高频、高速的数据传送问题,对阻抗匹配方面具有极高的需求。

DDR数据线可达每秒数千兆比特的传输速率,显著缩短了信号在线路上的传播时间。然而,若遇到阻抗失配情况,信号回波和干扰将极度加剧,从而引发数据传输失误。所以,DDR数据线对阻抗匹配有着极高的标准与要求。

阻抗匹配的基本原理

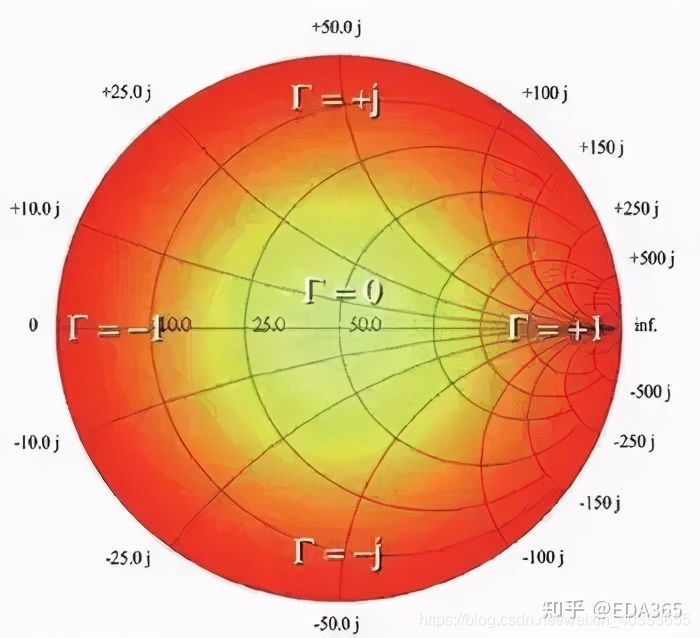

阻抗匹配原理并不深奥。常用的特性阻抗匹配方法使得传输线与负载阻抗相等,以确保信号无反射,降低损耗,提高传输效率。

实践运用中,常选用约为50欧姆的特性阻抗以达良好效果。此数值既能确保信号高效传递,亦可降低信号反射现象。然而,具体阻抗需结合实际电路设计与应用环境作出选择。

DDR数据线阻抗匹配的挑战

尽管阻抗匹配理论看似简单明了,然而其在DDR数据线中的实践运用却颇具挑战性。首先,鉴于DDR数据线极高的传输速率,对阻抗匹配精度提出了严格要求;其次,较长的DDR数据线使信号在传输过程中受到了更复杂的干扰因素影响。

实际上,DDR数据线的连接策略极其独特且复杂。在真实的电路板上,这些数据线与其他各类信号线、电源管线相互交错,使得阻抗匹配变得异常困难。面对这一问题,对此类数据线进行阻抗匹配时,必须采取专门的手段和技术解决方案。

阻抗匹配的常用方法

在实现DDR数据线上的阻抗匹配时,主要有以下几个方案可供选择。首要方案便是采用特征阻抗匹配方式——即使传输线路径的阻抗与负载阻抗达成平衡。此种手段简洁明快,然而对阻抗数值的精确度有着极高的要求。

接下来探讨的终端匹配法旨在在传输线路的末端附加一定阻抗。如此一来,在信号到达末端时可避免出现反射现象,从而显著降低反射率。不过这段流程可能会使电路结构略显复杂。

另一种办法为应用串连匹配策略。此法在传输线路头引入阻抗以避免初始段的信号反射,达成较少反射、增大学员的效果。然而,其随之而来的是信号衰弱值的提升。

阻抗匹配的实际应用

在实际的DDR数据线阻抗匹配过程中,普遍应用了多个策略。例如,我们可于线路之起点运用串联匹配,至于终点则实施终端匹配,以此有效降低信号的反射与衰耗程度。

为提升阻抗匹配精准度,我们运用特殊材料与合理结构。例如,采用特定绝缘材质以降低信号干扰,配合精巧布线设计降低信号反射发生率。

阻抗匹配的未来发展

伴随着电子技术的日新月异,阻抗匹配技术亦在稳步提升。展望未来,人工智能、机器学习等先进科技或将广泛运用于此领域,助推我们实现更精准的阻抗调控与更显著的信号反射衰减抑制效果。

随着5G、物联网等尖端科技的不断进步,阻抗匹配在电子工程领域的地位愈发凸显。可以预见,未来的电子工程师们,必将熟练掌握此项技术,以此推动电子业的创新发展。

阻抗匹配的常见问题

在DDR系列技术的阻抗匹配环节,我们时时面临着各种挑战,如信号的反射与串扰现象、信号强度的减弱以及电路实现难度的提升等。针对这些问题,我们需在实践中逐个攻克。

针对信号反射与串扰问题,采用终端匹配或串联匹配。对于信号衰弱问题,研发特殊材料及结构以降低其影响。至于电路繁复度问题,则借助特定布线架构简化线路设计。

阻抗匹配的实践经验

在实际执行DDR信号传输中的阻抗匹配时,积累丰富实践经验至关重要。例如,我们需熟知各种材料特性、不同构造的优劣以及各类技术应用场合。这些宝贵的经验将协助我们实现更为精准的阻抗匹配,从而更加高效地解决各类现实难题。

同时,持续探究和深入研究抗拒震荡技术以适应新趋势显得至关重要。唯有如此,我们方能紧随科技进步之步伐,提高抗拒振荡效果。

阻抗匹配的工具和技术

在实施DDR数据线阻抗匹配过程中,特定的利用行为和环保措施也必不可少。譬如,借助阻抗分析仪进行精准测量;运用仿真软件模拟阻抗匹配效能;以及运用自动化布线工具进行布线结构的精细调整。

应用上述工具及技术有助于精准操控阻抗,显著降低信号反射与衰减。此外,其亦助力实现更迅速的阻抗匹配,达到现实问题的高效解决方案。

阻抗匹配的案例分析

在实践中的DDR阻抗匹配过程中,我们有必要对几个成功的范例进行深入剖析及借鉴。例如,揭示并理解这些例子的成功因素,吸取其中的宝贵经验与策略。

通过对各项阻抗匹配案例深入剖析,从失败案例中学到教训,规避实践中可能出现的类似失误。通过这样的方式,我们有望更为精准地实施阻抗匹配操作,以更为高效地应对现实中的挑战。

阻抗匹配的未来展望

未来,阻抗匹配技术将会更加重要,更加复杂。

阻抗匹配的挑战与机遇

在DDR数据线的阻抗匹配研究中,虽然存在诸多难题与挑战,然而机遇同样并存。其中,精确度极高及电路极度复杂等问题构成了主要挑战,而技术发展空间巨大且创新方案繁多则成为了关键机遇所在。

通过深入的学术探究,我们能更高效地迎接挑战并抓住机会。

阻抗匹配的技术趋势

在DDR数据线连接过程中所涉及的阻抗匹配问题上,以下几点技术趋势需引起重视:一是随着精确性要求日益提高,电路变得愈发复杂;二是阻抗匹配领域的新技术层出不穷,如AI与机器学习等实用方法。

透析科技发展新趋向,有助于优化阻抗调节策略并有效化解实践难题。

阻抗匹配的未来挑战

未来,阻抗匹配技术将会面临更多的挑战。

这些挑战都需要我们在实际的阻抗匹配中加以解决。

阻抗匹配的未来机遇

未来,阻抗匹配技术将迎来诸多挑战与机遇。例如,随着人工智能和机器学习等新型技术的发展,阻抗匹配的创新空间逐渐拓宽。

阻抗匹配的未来发展方向

在未来,阻抗匹配技术将向更高精准度、更简化复杂度与更多创新方面迈进。通过持续深入的研究和学习,我们有能力提升阻抗匹配技术水平,有效应对实际工程难题。

我们需密切关注新兴科技如人工智能和机器学习的进展情况。

阻抗匹配的未来挑战与机遇

未来,阻抗匹配技术将会面临更多的挑战,但同时也充满了机遇。

阻抗匹配的未来技术趋势