对于尚未接触过DDR框架的读者,可能对此感到困惑。实际上,该图解旨在清晰展示DDR内存模块运作路径。DDR代表双倍数据速率,这一技术可提升数据传输效率。然而关于此图的具体内容及其所蕴含的奥秘,我们将共同深入理解探讨。

DDR框架图如同藏宝图,引领我们洞悉内存奥秘。此图囊括控制器、存储芯片及众多电路与接口等关键要素,每个环节均发挥着不可或缺之重要功能。若欲深入理解DDR内存运作机制,便须以上述框图为起点,逐步揭示其层层神秘面纱。

控制器,内存的大脑

DDR结构中,控制器发挥着关键作用,犹如内存的中枢神经系统,统领并协调各项操作。若失去控制器,内存将陷入混乱,如同无头苍蝇。其职责繁重,包括数据读取与写入、时序掌控以及错误检测等诸多方面。每一环节均需依赖于此,可见其责任之大。

控制器的运作机制相当精密繁琐。依据系统指令,严格管控内存每个细微步骤。在需求高速运行时,控制器需竭尽全力,确保数据即时输送;若系统发生错误,亦需其负责任何检验与修正,以保数据精度。此项作业,非寻常之人力所能胜任!

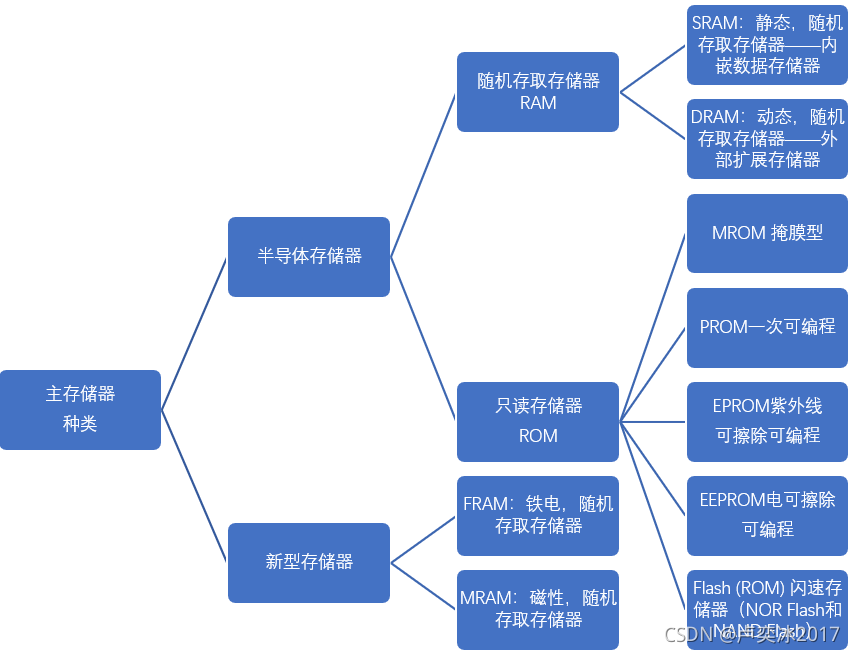

存储芯片,数据的家

在DDR框架中,存储芯片犹如数据之家,无论是图像、视像,还是文档、程序等诸类数据,皆需安身于此。其存储能力的大小将直接左右用户可容纳信息量的上限。如今市场所售的许多DDR内存产品,容量已从数GB至数十GB不等,可谓积沙成塔,日渐强大。

储存芯片运作机制深具趣味性。由于内部拥有无数微型储存单元,每个单元皆可容纳一位数据信息。这些单元以矩阵形式排列,利用行与列地址进行精确定位。当信息读取或者写入需求产生时,控制器随之指示相应地址,使得芯片迅速准确地寻址并执行相关操作。操作之迅捷令人瞠目结舌!

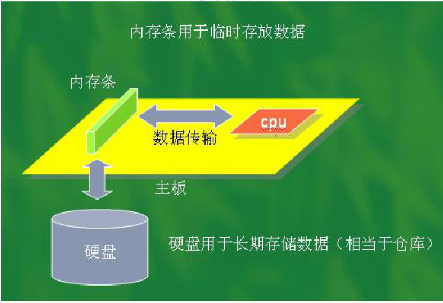

线路和接口,连接的纽带

在DDR框架中,线缆与端口作为桥梁,将各组件紧密相连。若无此链接,则无法实现控制器与存储芯片间的信息交互及数据传输。这些线路与端口犹如内存的神经网络,将各组件紧密结合。

线路与接口的设计须严格把控,需保障信号稳健传递且不受外部干扰。线路的长度、宽幅及材质均可能影响信号质量。接口设计亦需兼顾兼容性,以确保各类设备间的正常连接。此项工作,细节之处决定成败。

时序,时间的魔法师

于DDR架构中,时序至关重要,犹如掌控时间的魔术师,平衡数据传输之速率。时序的精妙设计,对内存性能产生直接影响。倘若时序设计稍有不当,将会拉低数据传输速度,从而对整个系统的顺畅运作构成挑战。

在时序设计过程中,需综合考量诸多因素,如数据从存储器传输至控制单元所耗费的时间以及控制单元处理信息所需时间等。此类延误必须精确测算以确保数据快速流畅地流转。此外,为提升性能,有时可采纳诸如预取和流水线等特定时序技术。此项工作涉及精密计算与操作,实属精细之举。

错误检测,数据的安全卫士

在DDR框架中,错误检测占据了至关重要的位置,犹如数据的守护者,确保其完整性不受损害。在数据传输过程中,诸如信号干扰、硬件故障等原因所导致的误差难以避免。若无错误检测机制,这些误差将悄然潜入数据之中,引发严重后果。

错误检监测方法多样,依次为奇偶校验法与CRC校验等。它们均能成功检测数据中错误,并予以更正。有时,为提升检监测精度,我们会运用如ECC校验等先进技术。此项工作,堪称数据安全的坚实保障!

性能优化,速度的追求

在DDR框架中,性能优化始终占据关键地位。犹如速度之追逐者,其驱动着内存技术持续前行。伴随着科技的进步,人们对于内存速度愈发苛求。历数自DDR1至DDR4的演进历程,每次更新换代皆实现了速度的显著提升。

多种途径实现性能优化,如提升时钟频率、扩展数据通道以及优化时序设计等。此类措施能显著增强存储器的性能,使数据传输更为迅捷。针对极速追求,特殊策略亦被采纳,例如超频与双通道技术等。此项事业赋予个体以速度之狂情感。

未来展望,技术的边界

DDR框图中的未来展望议题充满挑战与机遇,如探险家在未知领域发现新大陆,代表着内存技术的变革方向。科技推动下,内存技术历经DDR4至DDR5,乃至未来的DDR6跃进,每次升级均给人们带来惊喜与崭新体验。

内存技术的未来充满无限可能,如提升速度、扩大容量及降低能耗等都是其重要方向与世人所期待的成果。为求达成这些目标,甚至引入了前沿科技如三维堆叠和光学传输。此领域无疑是科技行业的明日新星。

总结,我们的探索之旅

在深度解析DDR框图过程中,我们精准洞悉了内存运作的机制,揭示出这个看似神秘的领域背后的奥秘。从控制单元至存储芯片,再到线路与接口以及时序和错误检测等各个环节,无不体现着其关键性和不可或缺性。而对于性能优化及未来发展的探讨,则进一步展现了内存技术的无尽潜力。

在此请问诸位:对于DDR内存还有何疑虑之处?欢迎广大读者于评论区畅所欲言,与我们分享你之独特观点见解。同是若您感觉此文颇具趣味性且具有参考价值,敬请不吝点赞并分享,让更多人参与这场探索之旅中来!