在FPGA技术领域,DDR内存配置无疑引人瞩目且充满挑战。初学者常常面临怎样设定DDR位数的难题,甚至可能因此而感到挫败。无需担忧,本文将为您揭示这一问题的答案,助您轻松掌握DDR位数设定技巧。让我们共同探索这一迷人领域,体验其中的乐趣与挑战。

一、DDR内存的基本概念

究其本质,DDR内存为高速数据传输之关键手段。采用DDR(双倍速率DataRate)技术,能在时钟脉冲上升沿及下降沿同步传输数据,从而大大提升数据的传输效率。将FPGA与DDR内存相结合,可助力实现更为高效的数据处理与存储。试想,当您的FPGA能流畅地与DDR内存进行数据交互,那份成就感岂不令人激动不已?

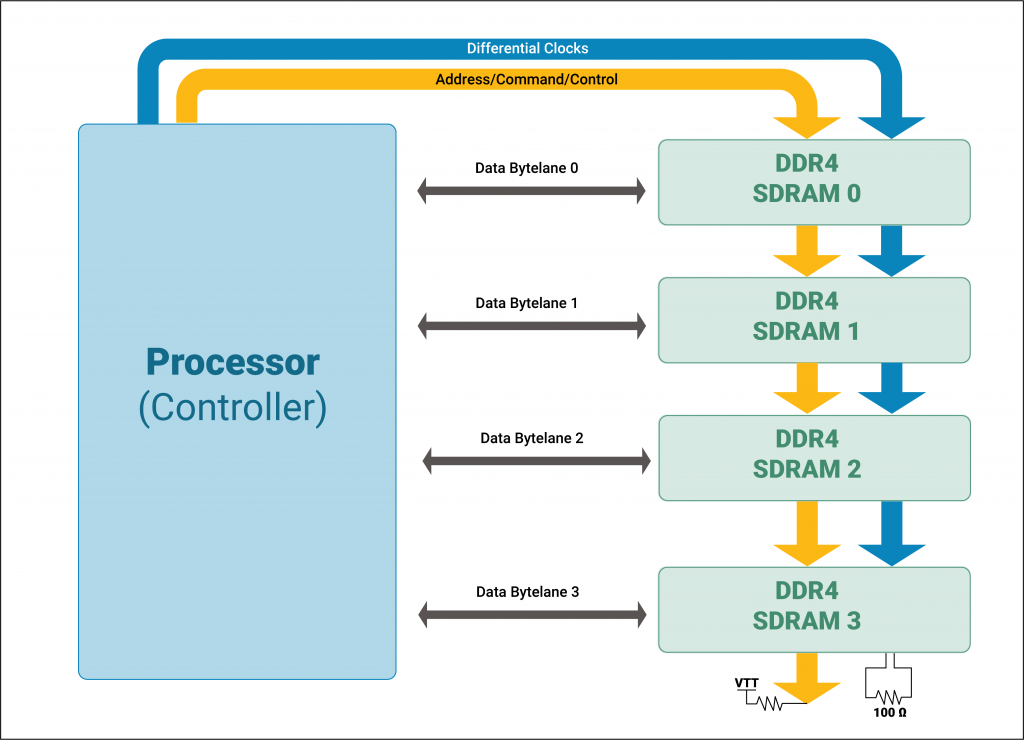

谈及DDR位数,即指内存带宽。市面上常有的DDR位数多为8位、16位、32位等。位数越高,数据传输量越大,然而设计难度与功耗亦随之攀升。此犹如一场权衡之术,需兼顾速率、成本与能耗。在此过程中,寻求FPGA与DDR间的最佳平衡至关重要,以实现两者的和谐共处。

二、选择合适的DDR位数

了解应用需求,确定DDR位数乃是首要任务。根据不同应用,内存带宽要求各异。若需处理大量图像或进行复杂计算,高位数DDR方能满足需求;反之,简单控制应用则可选用低位数DDR。此举犹如量体裁衣,选择最适宜之方案,方可事半功倍。

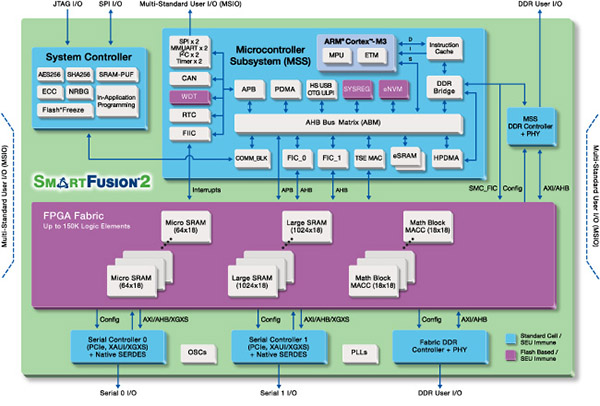

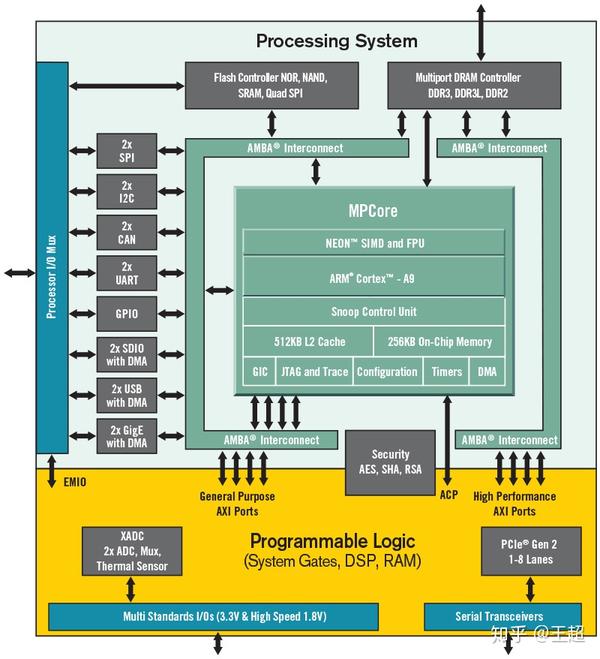

同时,为了充分利用FPGA资源,必须对DDR位数进行谨慎选择。基于每个FPGA芯片拥有独特的逻辑单元、内存以及输入输出端口极限,过高的DDR位数可能导致资源过剩或负荷过大,进而影响系统稳定性。因此,准确评估FPGA性能及适度选择DDR位数显得尤为关键。实践中,许多工程师会通过反复试验与调整,力争最佳解决方案。

三、设置DDR控制器的参数

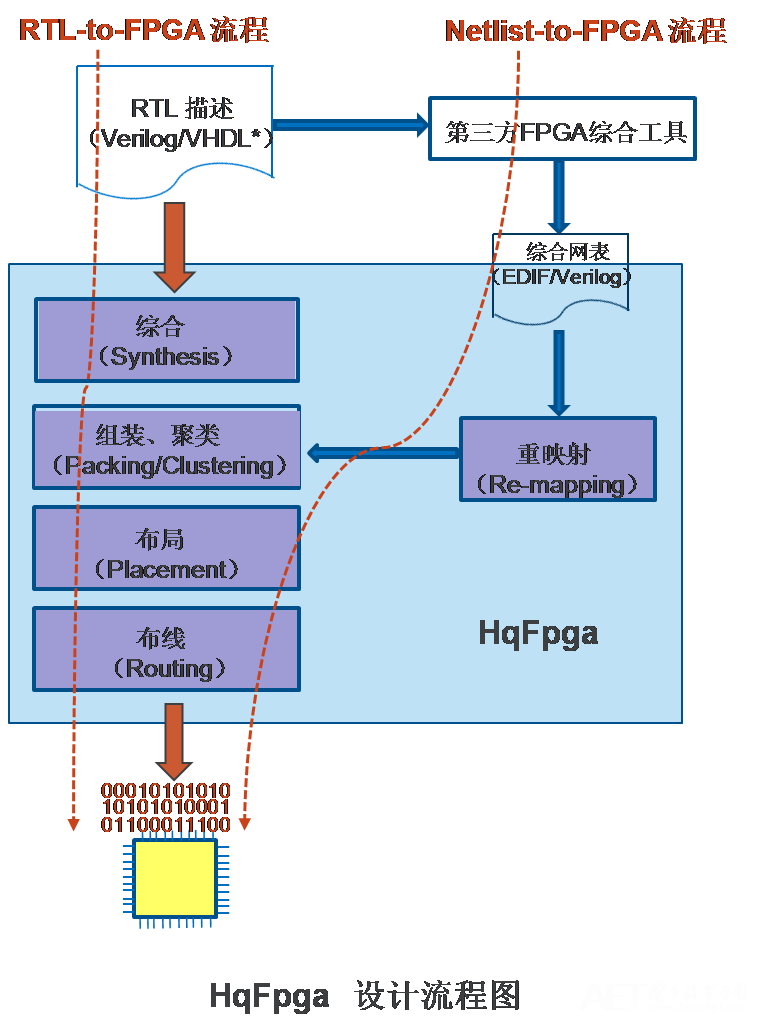

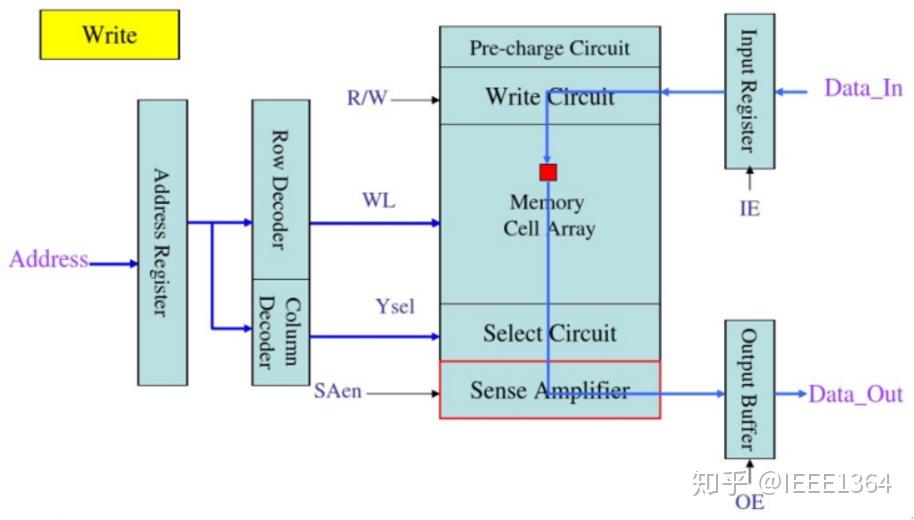

在选定DDR位数之后,接下来便是关键性的步骤——设置DDR控制器参数。此过程旨在建立FPGA与DDR间联系的枢纽,即控制器。一般而言,控制器设置涵盖时钟频率、延迟以及刷新周期等方面。这些参数的微调将对数据读写效率及稳定性产生直接影响。

调整时钟频率务必符合DDR内存规范,过高易引发信号干扰乃至系统故障,过低则影响DDR内存效能。因此,选择适宜的频率如同找寻开启FPGA与DDR高效连接的钥匙。

四、调试过程中的挑战

DDR的调试过程具有极大挑战性,即便设定了准确参数仍旧可能遭遇诸多问题,如信号完整性不佳及数据传输误差等。尽管这些问题令人困扰,但也正是这些挑战促使我们在探索中进步。

面临诸多技术难题,工程师们通常借助诸如示波器等设备深入剖析信号质量,以期找出潜在的干扰源头及故障所在。尽管这一过程颇为繁复,然而每逢问题得以解决之际,那份内心深处的满足感却是无法用言语形容的。在这些挑战之中,我们不仅提升了自身的技术水准,更深化了对FPGA与DDR之间复杂关系的认识。

五、优化DDR性能的小技巧

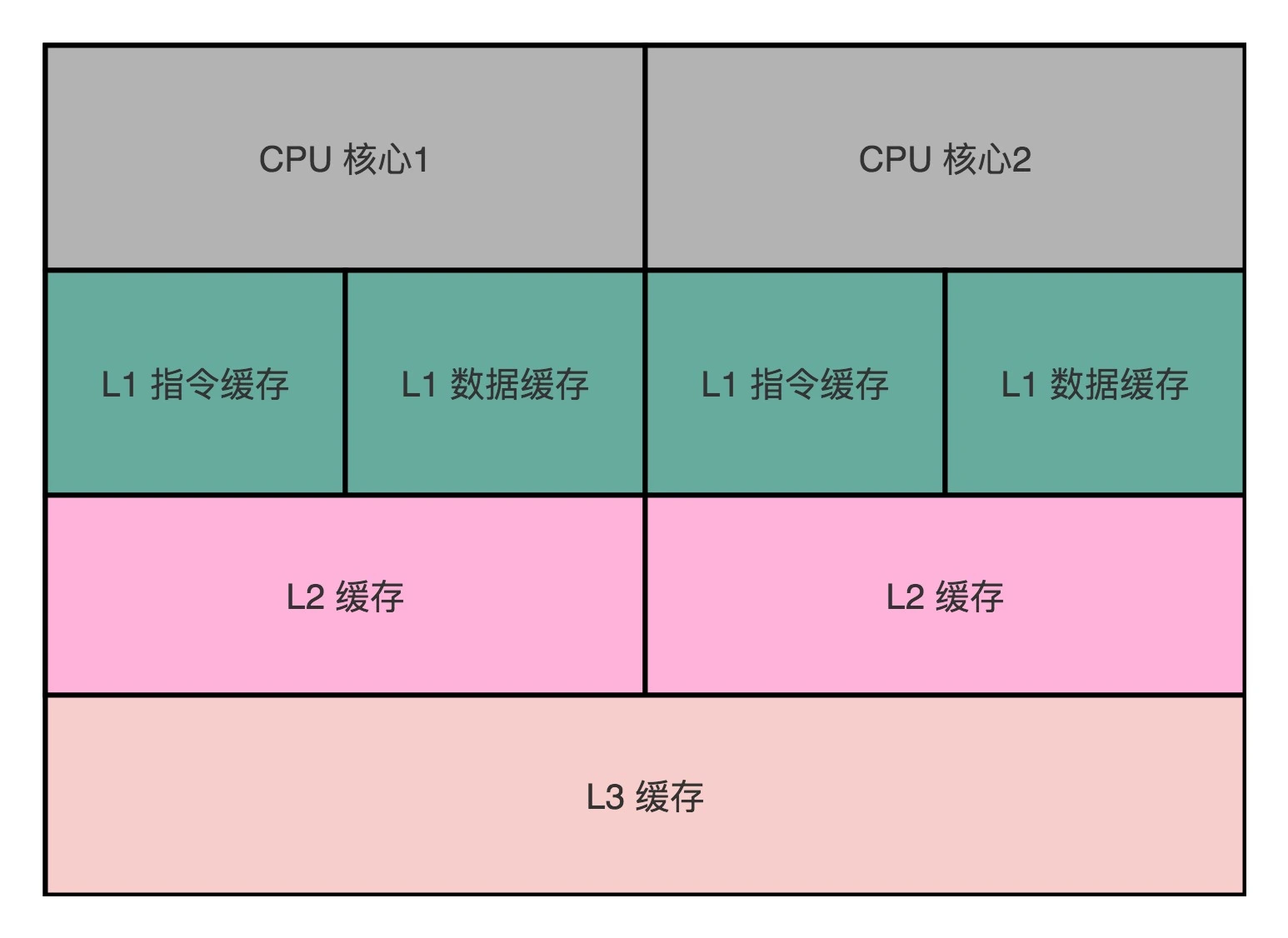

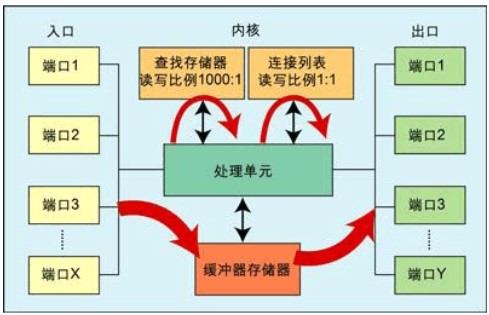

在调试环节,优化DDR性能备受瞩目,而简单的调整就可带来显著收益。譬如,优化数据读取与写入顺序,降低随机访问频率,这将极大地提升数据传输能力。再者,妥当的缓存管理方案也有助于实现总体性能的大幅提升。

适度运用时序约束,适时保证信号稳定性,可有效减少性能失误的可能性。透过这些精细化的调整处理,能使FPGA和DDR的配合更为协调流畅,并切实达成整个项目的预期效果。

六、总结经验教训

历经无数挫败与探索,我们从失败中汲取宝贵经验和教训。不论是挑选合适的DDR位数,设定控制器参数,抑或在调试过程中所遭遇的难题,皆为我们成长道路上的阶梯。每次失败使我们更接近成功,每次成功则赋予我们更多信心。

在此过程中,与同行业者进行深入的交流与分享至关重要。通过共同探讨及借鉴他人经验,我们能更迅速地寻找到有效的解决策略。尽管FPGA与DDR的融合充满了挑战,但这也是我们在科技领域持续探索和前进的动力源泉。

七、展望未来的技术发展

科技日新月异,FPGA与DDR的整合亦经历逐步变革。展望未来,我们可望迎来更为高效的内存技术、更智能化的控制单元及便利的开发工具。这些卓越的技术将为我们开拓无尽可能,助力于FPGA领域的创新发展。

作为技术领域的探索者,每个人无论新手或专家都以己之力推动着科技进步。坚信未来将更佳美好,让我们共同期待FPGA与DDR的再次傲世对决。