科技快速进步的当前时代中,DDR3及DDR4内存所涉及的PCB布线问题已然成了众多电子工程师关注的焦点。它们在数字电路中的地位无可替代,对整个计算机性能有着决定性的影响。无论玩家、设计者还是普通用户,皆希望获得更快的速率以及更高的效率。在此过程中,PCB线路担负着数据传输的重要任务。今日,笔者将带领诸位走进这个富有挑战且充满激情的领域,深入探讨DDR3与DDR4在PCB布线上的繁复细节与深刻思索。

一、DDR3与DDR4的区别

探讨PCB布线前,让我们了解下DDR3与DDR4之差异。DDR3内存工作频率常规为800MHz至2133MHz,然而DDR4已提升至上至1600MHz至3200MHz乃至更高速率。由此可见DDR4在数据传输速率上占据显著优势,从而能够迅速处理海量数据。此背景下,PCB布线设计亦不可避免地变得更加复杂。作为设计师,如何在狭小的空间中达到高效信号传输便成为重大难题。

除此之外,DDR4在工作时所需的电压更低,仅需常见的1.2V,相较之下,DDR3则需1.5V。这种改变不仅对电源设计产生影响,同时也对PCB布线的选择提出了更高的标准。以确保信号完整性为前提,设计师必须严格调整布线宽度和间距来适应不同的电压和频率需求。由此可见,DDR4的PCB布线设计复杂且充满挑战。

二、信号完整性的重要性

信号完整性在PCB设计中至关重要,特别是DDR3及DDR4布线上。在高速信号传递时,任何轻微干扰皆可能引发数据失误。故而,需通过运用差分信号传输、管控阻抗及良好地平面设计等方法,保证信号稳定性。其中所含的心力和智识,唯有实践者方能领悟。

对工程师而言,信号完整性的研究并非技术层面的课题,而是责任担当的表现。每一根布线上均承载着数据流,进而影响整体系统的运行效率。试想您畅游游戏世界之际,若因布线架构不合理导致延迟,那么那种体验无疑将是极不愉悦的.因此,每一位工程师都会在设计环节反复斟酌,精心调整,力图在每个细节上达到完美。

三、布线宽度与间距的选择

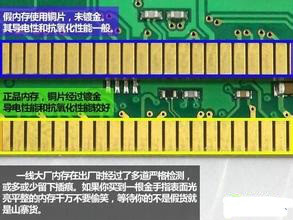

在DDR3和DDR4电脑板的布线上,控制布线宽度和间距极其关键。前者直接关联信号强度及载流能力,后者影响信号间的相互作用及对干扰的敏感程度。在高频率信号传输过程中,过窄间距容易引发串扰并对信号质量产生负面影响。

为此,设计师需依据需求进行科学计算与调适。针对高性能要求的应用情景,需扩大布线宽度以保障信号稳定;若遇空间受限状况,则需运用新颖的布线策略。在这看似矛盾的情况下寻得平衡,恰恰彰显了PCB设计的挑战所在。

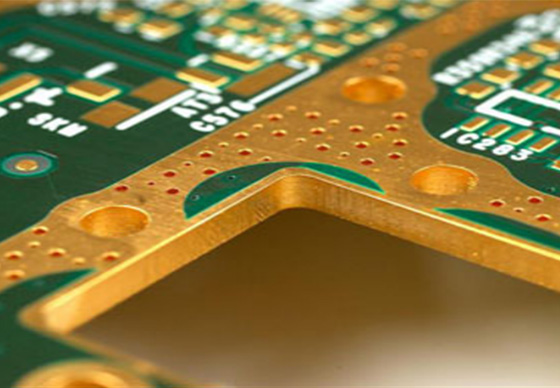

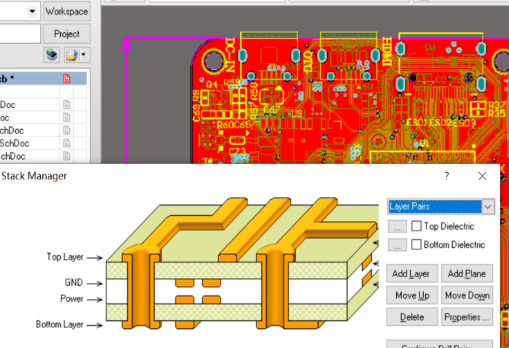

四、层叠设计的艺术

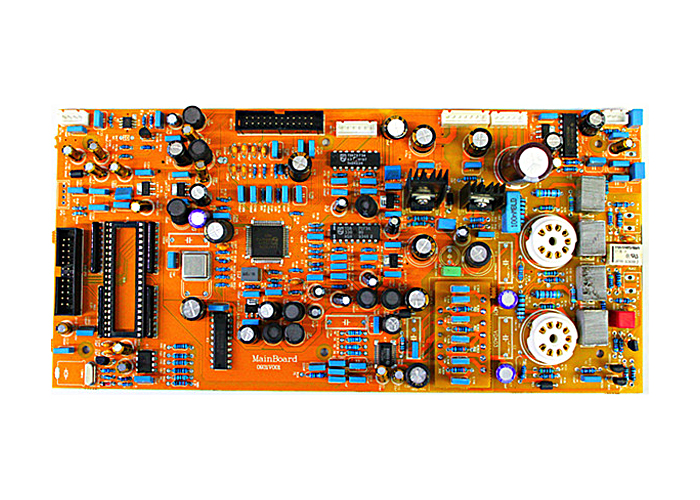

多层PCB布线的层叠设计至关重要。对于DDR3及DDR4类型内存,通过优化此设计可提升信号传输的稳定性并显著降低电磁干扰。工程师需在多层结构中合理安排信号、地层以及电源层,以实现优越的电磁防护性能。

在整个流程中,设计师执着于将其艺术才能和专业技能融为一体。每一层面板的设计均需经过周密策划,从原材料选取至层次划分,无不凸显出对每个细微之处的高度关注。试想,当您目睹一块精致完美的印刷电路板(PCB)时内心涌现的自豪以及成就感,而这些正是广大设计师所追寻并期望达到的。

五、温度管理的挑战

鉴于DDR3及DDR4版本的PCB布线工作中,温度管理的重要性不能被忽视,内存频率上升使得发热问题凸显,而拥有良好的散热途径则成为设计过程中的重大挑战。若温度过高,有可能致使内存运行性能下滑乃至局部器件损坏。故此,布线环节务必要重视散热通路的规划安排,以保证热量及时有效地排放出去。

实践中,设计师需协同各部门优选出最适宜的散热材料及其布置方案。此类跨职能的协作既提升了设计效率,又使每位成员深切体验到团队协作的优势。每次成功的散热设计都代表着对团队付出的肯定和激励。

六、测试与验证的必要性

测试与验证乃是PCB布线设计完结后必不可少之步骤。设计师务必借助全方位测试技术,以确保每根布线均符合预期性能指标。此举既是对自身职责的恪守,亦是为了提升用户使用体验。

在此过程中,设计师们往往遭遇突发性的困境。若遇测试中完美设计出现偏差,需立即查找并修正问题。尽管这一过程繁重紧张,却是设计师提升和进步的关键时刻。他们将每次失败和胜利都视作职业生涯中的宝贵财富。

七、未来发展趋势的展望

科技的飞速发展推动着DDR3和DDR4的PCB线路设计持续演进。展望未来,预计将出现性能更为优异的高频低压内存技术,这无疑对PCB设计带来新的挑战。为此,设计者需及时掌握新技能,应对未来发展。

趋势所趋,PCB设计将紧密关注集成和效率,要求设计者在技术环境日益复杂的现状下寻求最优解,这不仅是对其技能的检验,也是对创新精神的考量。面向未来,设计师应保持积极心态,勇往直前,迎接各类新挑战。