身为专职电子工程师,我对DDR3布局有深厚领悟及丰富经验。本文旨在Embracing DDR3 Layout之奥秘,引领读者深度探求此领域。于此,从基础原理至实战布局技巧逐一解析,揭开其神秘面纱。

什么是DDR3?

首当其冲,需对DDR3有清晰认识。作为 Double Data Rate 模式下的动态随机存取存储器(DRAM),DDR3为DDR2的次世代产品,具备更快的数据传输能力及更低的能耗,常用于各类计算机系统、伺服器和嵌入式装置中。在DDR3布局设计阶段,务必关注信号完整性、时间顺序校正以及能耗优化等关键环节。

如何进行DDR3布局规划?

在实施DDR3布线计划过程中,首要任务为确保信号传递路径无误,以及保证时序同步性。通过精确设定信号线走向及长度,合理划定各级供电区域,运用恰当的阻抗匹配技术,是非常关键的步骤。同时,也必须重视时序校正问题,包括延时匹配,时钟树架构设计,数据对齐等多方面内容。

DDR3布局中的信号完整性问题如何解决?

在DDR3布线设计过程中,必须重视信号完整性这一关键因素。为保证信号品质稳定,应采取多种技术手段应对信号完整性问题。如减少串扰、防止反射及回波,精心布置电源与地网以降低功耗噪音以及选取相应的阻抗匹配策略提升传输效率等。

DDR3布局中常见的容易出错的地方有哪些?

设计实践中需警惕频发的易错环节,如时序配对失误产生数据错误,信号路径安排不当引发串扰,或供电/接地系统制订不当诱使功耗起伏等。故而DDR3布局规划之际,技术人员务必对每个细节严格把关,预防此类通病。

如何优化DDR3布局以提高性能?

为了提升DDR3系统的性能表现,可从以下几个角度进行深度优化:首先,设计一个合理的电源供应网路,有效降低噪音危害;其次,引入差分对以强化抗干扰能力;第三,优化时序校正策略以进一步提高数据传输速度;最后,运用仿真评估工具,对布线进行准确调校。以上举措皆有助于持续改善DDR3系统性能。

DDR3布局中需要注意哪些EMI/EMC问题?

在完成DDR3布局设计的同时,亦需重视电磁干扰(EMI)以及电磁兼容性(EMC)等关键因素。我们将通过合理规划电路路径、强化屏蔽与接地处理及择选低噪元件等策略降低系统对外界干扰的敏感程度,以保障其在复杂电磁环境中的稳定性和可靠性。

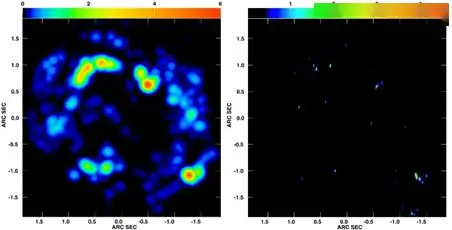

如何利用仿真工具辅助DDR3布局设计?

在实践中的DDR3布局设计环节,仿真工具发挥着举足轻重的作用。凭借其精准的模拟效果,能够深入了解信号传播路径、时序校准状况及功耗分布等关键信息,迅速识别出可能存在的隐患,从而针对性地改进和优化设计方案。因此,在进行DDR3布局设计时,充分运用仿真工具将极大提升设计工作的效率与可靠性。

如何评估和验证最终的DDR3布局效果?

在圆满完成DDR3布局设计之后,下一步的关键步骤便是对其进行全方位的评价与确认。这包括利用实体PCB样品制造、信号连续性检测、能耗计量及系统联合调试等多元化技术方式,验证DDR3布局是否达到了理想的运行性能,同时及时修正并优化,保证最终交付至客户手中的产品能够满足他们的需求。