在当前科技进步迅猛的背景下,DMA(直接内存访问)、DDR(双倍数据速率)以及FIFO(先进先出队列)在众多电子设备与计算机系统中扮演着核心角色。它们之间既相互依存,又各自具备显著的功能特点。

DMA的基本概念

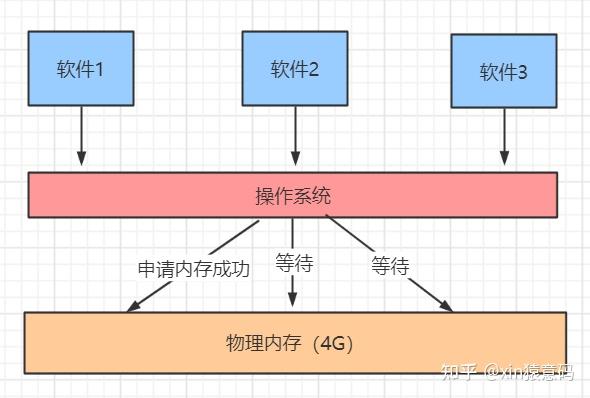

DMA技术是计算机系统中的一个关键机制,它允许设备直接对内存进行操作,无需经过CPU的频繁介入。这一特性显著提升了数据传输的效率。例如,在磁盘存储与内存之间的数据交互中,若采用传统方式,即通过CPU进行数据转发,将导致CPU负载加重,传输速度降低。此外,DMA在多媒体处理领域同样扮演着至关重要的角色。对于音频、视频数据的采集与播放,DMA技术确保了数据能够在设备与内存之间实现快速且流畅的流动。

DMA技术对于众多对实时性有高度要求的场景至关重要。在诸如工业控制系统等场合,传感器所获取的数据必须迅速写入内存以供计算,DMA技术恰能高效实现这一功能。

DDR的原理及特点

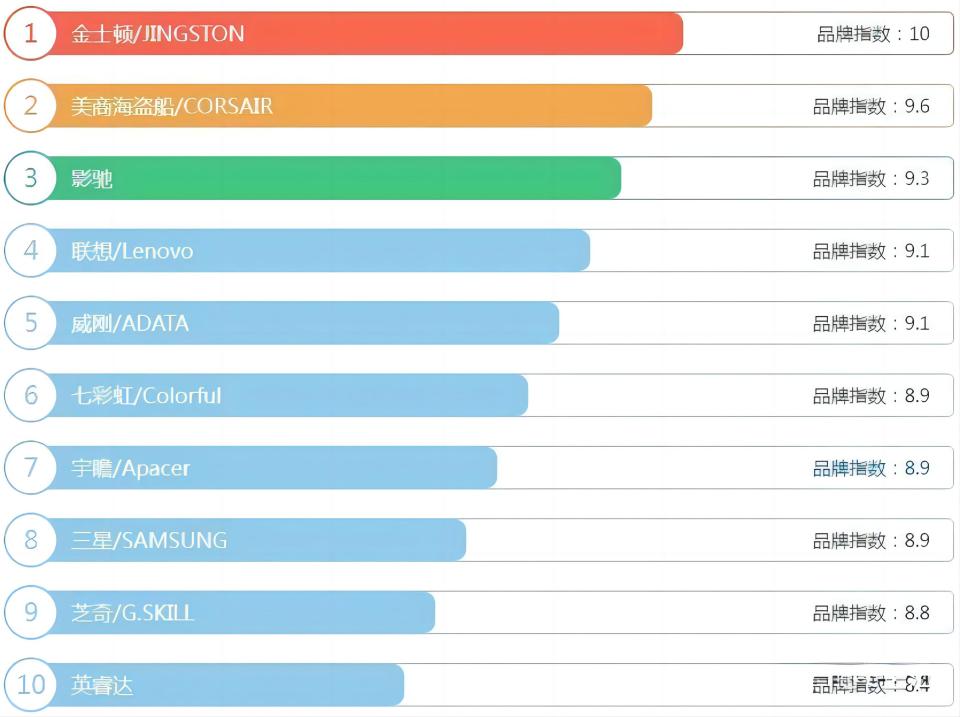

DDR技术显著增强了内存数据的传输效率。其核心原理在于,DDR技术通过实施双倍数据速率策略,在时钟信号的上升和下降两个阶段均能完成数据传输,从而显著超越了传统内存的传输速度。以一款常规内存为例,在相同频率条件下,DDR内存的传输速率几乎可以达到传统内存的两倍。此外,DDR技术的频率特性同样至关重要,高频率虽然能提供更快的传输速度,但同时也需兼顾硬件的稳定运行和兼容性。在当今的计算机系统中,DDR内存的持续迭代升级,对整体系统性能的提升起到了至关重要的作用。

DDR技术的应用领域极为广泛,以游戏专用电脑为例,高速的DDR内存能够显著提升游戏在场景加载、纹理读取等环节的运行效率,有效降低运行过程中的卡顿现象。在图形工作站领域,DDR的高速性能对于快速处理大规模图像及渲染任务尤为关键。

FIFO的功能与模式

FIFO的核心作用是基于先进先出的原则对数据进行有序管理。在数据处理转换过程中,FIFO充当了缓冲器的角色。比如,在处理速度各异的数据模块间,FIFO能够暂时存储数据,有效防止数据遗失。当存在一个数据生成速度快于处理速度的模块时,FIFO能够实现数据的平滑过渡。此外,FIFO具备多种读写模式。在同步FIFO模式下,读写时钟保持同步,这种模式在简单内部电路数据缓冲中较为普遍。而异步FIFO则适用于读写时钟来源不同的场景,常用于芯片或模块间的通信缓冲。

在具体的项目实施过程中,例如网络数据包的加工环节,接收到的数据包呈现非规律性,它们需首先被存入先进先出队列(FIFO),并依序接受后续的解析与处理。若缺乏此队列,将可能导致数据接收与处理流程的混乱。

DMA与DDR的协同工作

DMA与DDR通常协同运作以优化系统效能,其中DMA能够直接对DDR进行数据的读写操作,从而实现数据快速转移至其他设备或反之,如手机拍照时,DMA可直接将摄像头采集的数据写入DDR内存,大幅提升效率。同时,DDR的高效特性亦依赖于DMA的高效传输机制以充分发挥其性能。若缺乏DMA,CPU需承担在DDR与设备间传输数据的工作,将导致CPU负担过重。

以一例说明,于视频播放设备内部,视频资料预先存储于DDR存储器中。在播放过程中,借助DMA技术迅速将数据传输至解码器等关键部件。此举确保了设备运行的高效与稳定,进而为用户带来了流畅的观影感受。

DMA与FIFO的关联

DMA与FIFO之间存在着紧密的互动关系。在众多应用场景中,DMA能够直接从FIFO中读取或向其写入数据。比如在众多微型嵌入式系统中,外部传感器的数据首先被存储在FIFO中,随后通过DMA技术传输至内存以进行后续的分析等处理。在此过程中,FIFO充当了数据临时存储的关键节点,确保了数据传输的有序性。

此外,在多设备共用DMA通道的情况下,FIFO机制能有效减轻因数据传输而产生的不一致。以配备多个传感器的物联网设备为例,各传感器收集的数据首先被存入FIFO缓存,随后依照既定次序经DMA通道进行数据迁移与处理,以此避免数据冲突的发生。

DDR与FIFO的交互

数据传输过程中,DDR与FIFO各自采用独特的方法。FIFO能够从DDR中提取数据缓存,尤其是在进行大规模数据传输操作时。以服务器数据处理为例,众多数据首先从硬盘读取并暂存于DDR,随后根据实际需求,将部分数据选入FIFO以实现缓冲,以便进行后续处理。

FIFO机制还能够将部分处理成果及数据信息反向写入DDR存储器。在那些对数据存储周期较长的处理结果应用场景中,FIFO扮演着类似接力棒的职能,依据DDR的存储规范,将数据有序传输至对应的内存区域以实现存储。

本文旨在使您对DMA、DDR及FIFO技术有更为透彻的认识。若您在此领域有所经验或存有疑问,敬请于评论区互动交流。若您认为本文内容优质,不妨点赞并予以转发。