DDR,即双倍数据率,在众多数字系统中扮演着核心角色。在运用Vivado工具的过程中,DDR的生成步骤既繁琐又至关重要。这一过程需要细致的设置和深入的理解,包括但不限于IP核的选用以及相关参数的调整。每一个步骤都直接关系到DDR能否被正确生成。

DDR简介

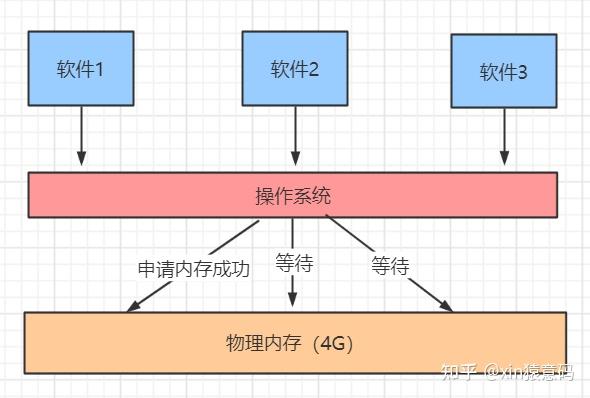

DDR,即一种高速的数据存储与读取技术。在现代电子系统中,诸如FPGA(现场可编程门阵列)等设备,DDR能显著提高数据处理速度。它通过双倍数据速率传输,允许在时钟的上升沿和下降沿同时传输数据,这与传统方式大相径庭。此外,DDR在硬件上还具备独特结构,这些结构使其能够实现高速的数据读写。在高速数据采集与处理系统等实际工程应用中,DDR的作用至关重要,不可替代。

DDR的工作原理决定了其特性。比如,它的时序要求极为严格,目的是确保数据能在恰当的时刻被存储和读取。若时序出现偏差,可能引发数据错误或系统不稳定。这对工程师来说是个挑战,因为设计时需精确考量各种因素对时序的影响。

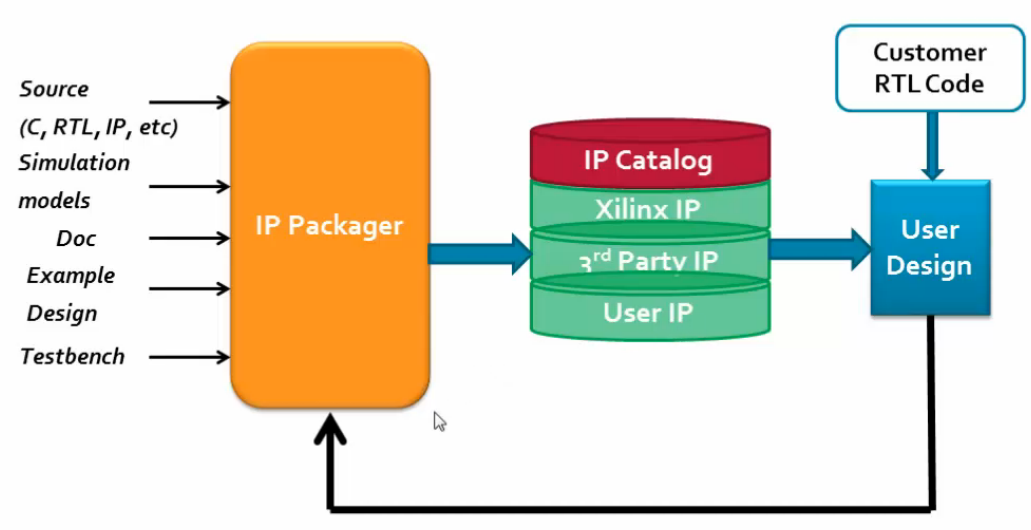

Vivado中的IP核

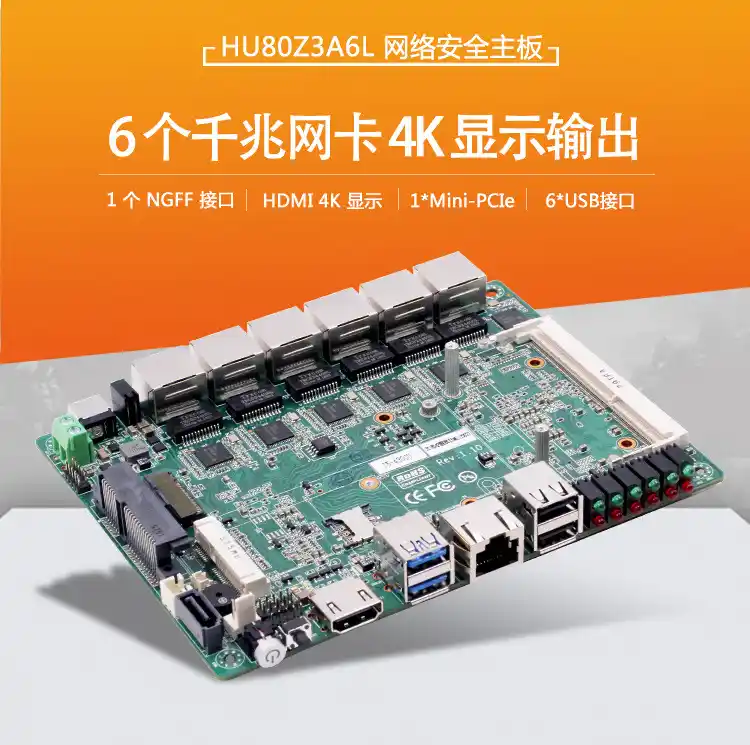

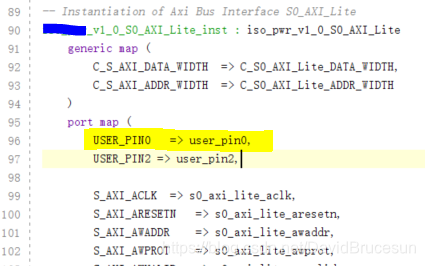

在Vivado软件中,若要创建DDR,必然需要使用IP核。IP核,即知识产权核,是一种预先设计好的、可重复利用的电路模块。Vivado特别为DDR提供了相应的IP核。这些IP核具有很高的可定制性。在使用DDRIP核时,首先要根据实际硬件资源的情况,挑选恰当的DDR类型。比如,若FPGA硬件支持DDR3,那么在IP核的配置中,就应该选择DDR3的相关设置。

Vivado的不同版本对IP核有所更新和优化。新版本可能支持新的DDR类型或更高性能。此外,IP核的参数配置非常丰富。例如,数据宽度、存储容量、读写频率等参数需根据实际应用场景进行设置。这些参数的准确性直接关系到DDR在系统中的工作表现。

参数配置

DDR在Vivado中的参数配置至关重要。数据宽度是其中的一个关键参数。它决定了每次传输的数据量。若数据宽度设置偏小,传输效率将受影响;若设置过大,则可能超出硬件支持范围。此外,存储容量的设置同样重要。这一设置需与系统整体需求相契合。

这些之外,读写频率的设定同样十分关键。读写频率若过高,可能引发时序问题;若过低,DDR的高性能就无法得到充分发挥。在具体配置这些参数时,必须参照芯片手册并结合工程的实际性能需求。以高清视频处理系统为例,由于数据量庞大,合理调整这些参数是确保DDR高效处理数据的必要条件。

时序约束

时序对DDR的稳定运行至关重要。在Vivado软件中,必须确保时序约束的准确性。时序约束决定了信号间的时间联系,这包括时钟信号与数据信号之间的关联。比如,数据的建立与保持时间必须在指定时钟周期内完成。若未正确设置,数据在传输时可能会出现错误。

同时,不同的DDR类型对时序约束的要求各异。设计人员需在Vivado中精确地根据所选DDR类型进行时序约束的详细设置。这是确保DDR稳定运行的关键。特别是在一些通信系统中,由于需要长时间稳定传输数据,对DDR的时序约束设置必须做到精确无误。

验证与调试

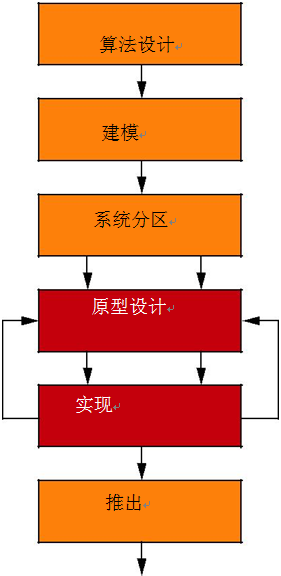

完成DDR生成设置后,验证和调试工作显得尤为重要。Vivado为我们提供了一系列工具,以辅助我们进行验证。首先,我们可以进行功能仿真。通过功能仿真,我们能够检验DDR的逻辑功能是否准确,比如数据的读写是否达到预期效果。一旦在功能仿真过程中发现问题,我们便能及时返回并调整参数。

功能仿真之外,还有时序仿真可供选择。这种仿真更贴近真实工作状态。它能检验DDR在时序约束条件下的运行状况。若时序出现异常,或许需对时序约束进行调整,或是对硬件连接进行检查。在项目开发过程中,许多潜在问题往往是在调试过程中被揭示的。

实际应用中的注意事项

在实际的工程应用中,我们还需留意一些细节。例如,DDR周边电路的设计至关重要。该电路必须保证电源稳定,信号匹配得当。若电源不稳定,DDR的性能将受影响,甚至可能无法正常运作。

此外,DDR模块间的交互同样不容忽视。比如,它与数据处理模块间的数据传输接口便是一个关键点。设计时必须确保接口既兼容又准确无误。在用Vivado生成DDR的过程中,你是否遇到过什么特别棘手的问题?不妨在评论区分享一下你的经历,同时,也欢迎点赞和转发这篇文章。