DDR(双倍数据速率)测试架构构成了DDR测试领域的核心要素,其涉及信号完整性、测试精确度等多个关键领域。为便于深入阐述,本文将对其内容进行细致划分,并分述为六个独立章节。

DDR测试拓扑的基本概念

DDR测试连接方式模型即DDR测试拓扑,其核心作用在于详述测试连接的布局。在硬件设计过程中,采用恰当的测试拓扑对于确保测试结果的准确性至关重要。以主板DDR电路的简单测试为例,若拓扑设计不当,将可能引发信号反射等测试问题。究其原因,不同拓扑结构对信号传播的干扰程度各异,这是DDR测试中不可或缺的考量因素。此外,DDR测试拓扑与硬件的布局布线亦紧密相连,唯有合理的布局布线,方能充分发挥拓扑结构的效能。

确保DDR测试的拓扑结构能够模拟出被测设备在实际应用中的运行状态。以高密度服务器主板为例,其中DDR芯片与CPU之间的连接拓扑往往相当复杂。若测试所采用的拓扑结构与实际应用情况不一致,则所收集的数据将存在误差,无法真实反映DDR组件在实际使用中的性能表现,进而可能导致产品上市后出现兼容性及性能上的诸多问题。

常见的DDR测试拓扑类型

点对点拓扑结构为一种普遍采用的布局模式,其显著特点为信号路径的直观与简洁。在针对小型嵌入式设备进行DDR性能测试时,点对点拓扑能够有效追踪并识别信号传输环节中可能出现的故障。得益于设备体积的限制,信号干扰因素相对有限,从而使得该拓扑结构在满足性能测试方面表现出色。然而,其应用范围亦存在限制。在大型设备或复杂电路系统中,点对点拓扑可能无法满足众多连接点的需求。

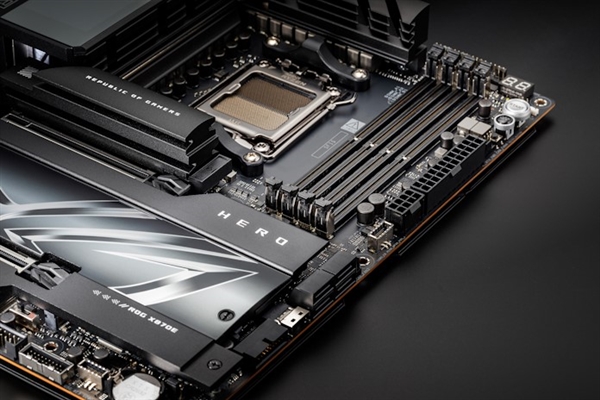

存在一种称为星型拓扑的连接方式。在多芯片DDR测试的情境中,类似于某些高端主板上,多个DDR芯片环绕一个控制核心的配置,便呈现出了星型拓扑的特征。这种结构便于对多个DDR模块的信号传输与测试状态进行有效管理,然而其结构相对复杂,配置测试参数亦相对繁杂。若中心节点发生故障,将可能对整个DDR测试系统造成影响。

DDR测试拓扑中的信号完整性

首要任务是确保信号线的长度精准匹配。在DDR测试的拓扑结构中,若信号线长度存在差异,将引发信号同步性的问题。以笔记本电脑的DDR测试为例,若某根信号线长度超出标准,将导致信号传输延迟,从而不可避免地影响数据传输的精确度。因此,在设计测试拓扑时,必须对信号线的长度进行严格把控。

信号串扰现象亦不容忽视。尤其在DDR测试拓扑结构中,多条信号线并行布线,尤其是线路密度较高的情形下,串扰现象尤为显著。例如,在服务器内部DDR模块的测试过程中,串扰可能导致信号严重畸变。因此,必须对线路间距进行科学规划,并采取屏蔽线等手段,以在DDR测试拓扑中确保信号完整性的提升。

DDR测试拓扑与硬件组件的关系

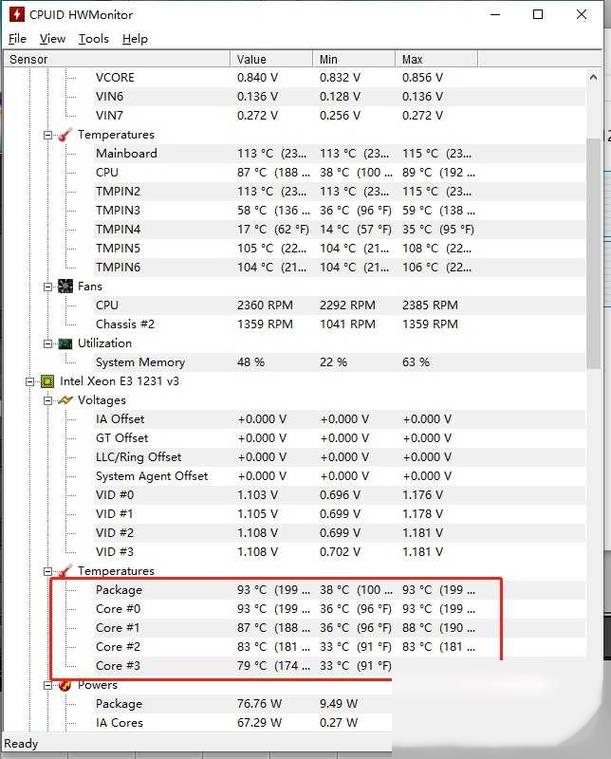

CPU对DDR测试拓扑的布局具有显著影响,其核心原因在于CPU作为DDR数据交换的核心调控单元。不同种类的CPU对DDR测试拓扑的需求各异,必须与之相匹配。以高性能桌面CPU为例,它们通常需要配备能够高效、稳定传输大量数据的DDR测试拓扑。若不匹配,就如同以小马拖大车,将导致整个系统运行速度大幅降低。

主板作为DDR模块的承托平台,对测试结构的布局亦提出特定要求。主板的具体尺寸与层数等硬件属性,将直接作用于DDR测试结构的搭建。这如同在有限的空间范围内,必须精心规划DDR元件与测试接口的布局,若设计失当,将给DDR测试的后续步骤带来诸多挑战。

在实际工程中构建DDR测试拓扑

首要任务是进行需求剖析。需明确测试的根本目标为何,系性能评估、兼容性检验抑或其他。以一款新型手机主板研发为例,需针对其DDR功耗需求进行测试架构的规划。此过程需充分考虑测试设备的连接方式,以确保对功耗的测量精准无误。

在实施第二步过程中,需对硬件资源进行统筹规划。依据现有硬件设施与元件,精心设计出最适宜的DDR测试架构。如在部分小型企业的研发阶段,鉴于硬件资源相对匮乏,可能需采纳更为简洁高效的DDR测试架构,以此实现成本节约并满足测试要求。同时,还需关注硬件设备的采购可行性,以防止因某些关键元件难以获取而使测试架构难以执行。

DDR测试拓扑未来的发展趋势

技术进步推动下,测试拓扑正逐步向智能化演进趋势迈进。以自动化测试设备的持续升级为证,DDR测试拓扑正逐步整合自感应和自适应功能。在众多电子产品生产线上实施DDR测试过程中,智能化的拓扑结构能够更迅速、更精确地判定DDR模块的性能状况,从而有效降低人力成本。

简洁高效的发展方向之一显现。伴随着DDR技术持续演进,其内部组件的集成度不断提升,因此DDR测试架构亟需简化其繁杂的结构,转而采纳更为简洁高效的连接策略,以适应对高速及高容量数据传输测试的迫切需求。

在DDR测试过程中,你是否遭遇过难以克服的拓扑问题困扰?我坚信众多读者在此领域存有诸多疑问,若本文对你有所助益,敬请给予点赞与转发支持!