DDR编码排版是一项专业性较强的技术领域,它关联着数据的储存、传输以及相关设备性能的稳定性等多个方面。这一领域内包含了众多复杂的规定和技术关键点,对于从事计算机硬件和数据处理工作的人员而言,具有极其重要的意义。

DDR编码的基础概念

DDR编码,即双倍数据速率同步动态随机存取存储器的编码技术。本质上,它是一种提升数据传输速度的方法。与传统内存不同,它允许在时钟周期的上升沿和下降沿同时传输数据,显著提高了传输效率。这种编码方式对时序要求极高。为确保数据的稳定准确传输,电路等硬件设计必须与之相匹配。

DDR的编码速度在不同代产品间存在明显不同。比如DDR3和DDR4,随着代数的提升,数据传输速度逐渐加快。同时,编码方式也在不断进步,目的是为了满足更高带宽的需求。

排版中的数据结构

在DDR编码排版中,数据结构扮演着基础框架的角色。DDR中的数据采用特定的位模式进行存储与传输。通常,它包括行地址、列地址等信息的有序安排。这些数据结构不仅决定了内存可以容纳的数据量,还影响了如何快速定位特定数据。

在实际应用中,若数据库管理员希望优化服务器内存使用,就必须深入掌握DDR数据结构的特性。错误的数据结构可能会引起数据冗余或读取速度减慢。以不合理排列为例,当需要获取特定数据时,CPU可能需要耗费更多时钟周期来定位,这无疑会影响到整个系统的性能。

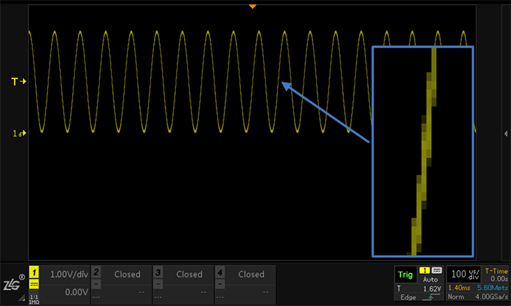

信号完整性与编码排版

信号完整性与DDR编码的排版紧密相关。在DDR进行高速数据传输时,若信号完整性遭到破坏,比如出现信号反射或串扰等问题,编码排版所设计的传输数据将无法正常进行。为确保信号完整性,我们在进行PCB布线时必须遵守一系列规定。

在硬件电路板上,务必减少传输线的长度,同时布线时保持适当的间距,这些都是确保DDR编码排版正确实施的关键。若不如此,即便编码本身准确无误,信号的不稳定仍可能导致最终结果出现数据错误。

电压与DDR编码排版

在DDR编码排版中,电压设定是一个不容忽视的环节。不同的DDR模块对工作电压的要求各异,比如DDR3可能需要1.35V或1.5V的电压。这一电压设定必须精确无误,否则电压过低可能引起数据传输不稳定,甚至导致无法正常工作。

实际操作中,组装电脑时,主板必须为DDR内存提供适宜的电压。若主板选择不当,或是BIOS电压设置有误,可能会导致系统崩溃,或是内存运行降频。这一点充分说明了电压在DDR内存实际应用中的关键作用。

时序约束与编码排版

在DDR编码排版中,时序约束十分严格。这要求数据必须在时钟沿的特定时间段内完成有效的传输。这包括数据建立时间和数据保持时间等具体要求。这些时序参数与DDR的编码紧密配合。

在设计DDR硬件电路的过程中,电路设计者需严格遵循时序约束,以保证数据传输的准确性。以一款高端服务器内存板为例,若时序约束不够精确,数据可能在错误的时间被读取或写入,进而导致数据错误或系统故障。

错误检测与校正机制

在DDR编码排版过程中,一般都设有错误检测与校正机制。这一机制旨在确保在数据传输与存储环节,能够有效应对各种干扰和故障,从而避免错误的发生。其中,ECC(ErrorCorrectingCode)便是常见的错误检测与校正码之一。

在现实生活中,服务器所使用的DDR内存往往需要配备ECC功能。这是因为服务器对数据的准确性有着极高的要求,哪怕是微小的数据错误也可能带来严重后果。比如,它可能会导致数据中心客户的数据出现混乱甚至丢失。

在工作中或学习时,你是否遇到过与DDR相关的信号完整性问题,或是数据结构上的难题?欢迎在评论区告诉我们你的经历。同时,别忘了点赞并转发这篇文章,让更多的人受益。