FPGA中的DDR驱动,也就是双倍数据速率驱动,这部分相当复杂且至关重要。DDR在FPGA的各种应用场合中扮演着重要角色。它能够提供高速且稳定的数据存储和读写能力。这对于实现高速数据缓存、大型数据处理等功能至关重要。要想提升整个FPGA项目的性能,理解和掌握DDR驱动是非常有帮助的。

理解DDR

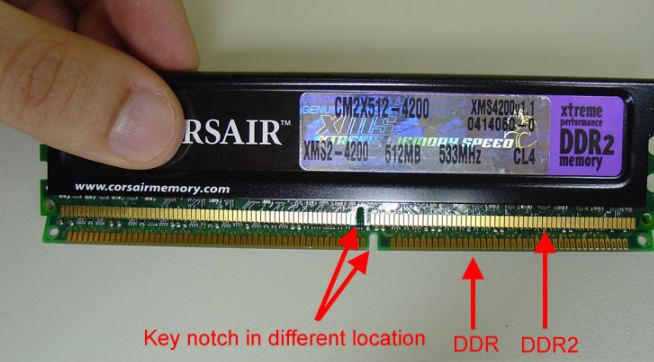

DDR,一种高速同步动态随机存储器,其独特之处在于能够在每个时钟周期的上升和下降沿同时进行数据传输。这种传输速度相较于一般内存有了显著提升。在众多大型服务器中,为了高效处理大量数据,它们普遍选择依赖DDR卓越的数据读写能力。FPGA与DDR之间的数据交互严格遵循信号协议,确保了数据传输的稳定性,并实现了高速率的数据传输。此外,DDR内部存储单元的结构设计,使其能够高效存储数据并迅速响应请求,这也是其作为高速存储器的一大优势。

在硬件设计上,DDR的引脚布局和信号定义遵循着严格的规范。以DDR3为例,地址线、数据线和控制线各自承担着不同的任务。地址线负责定位存储单元,数据线负责传输数据,而控制线则负责协调数据的读写。FPGA若想正确驱动DDR,就必须清楚各类引脚的功能并准确连接。电路连接上的任何小错误,都可能使DDR无法正常工作,甚至导致其工作不稳定。

驱动开发流程

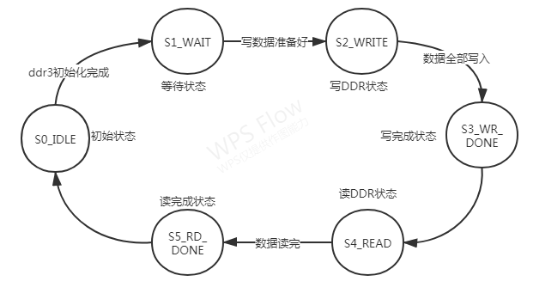

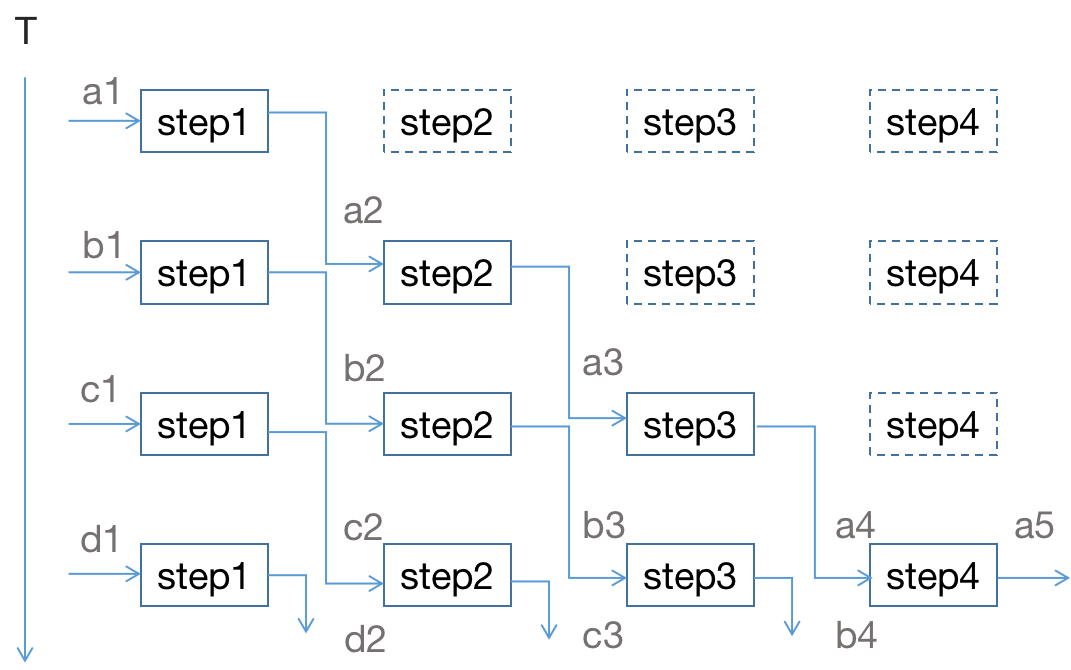

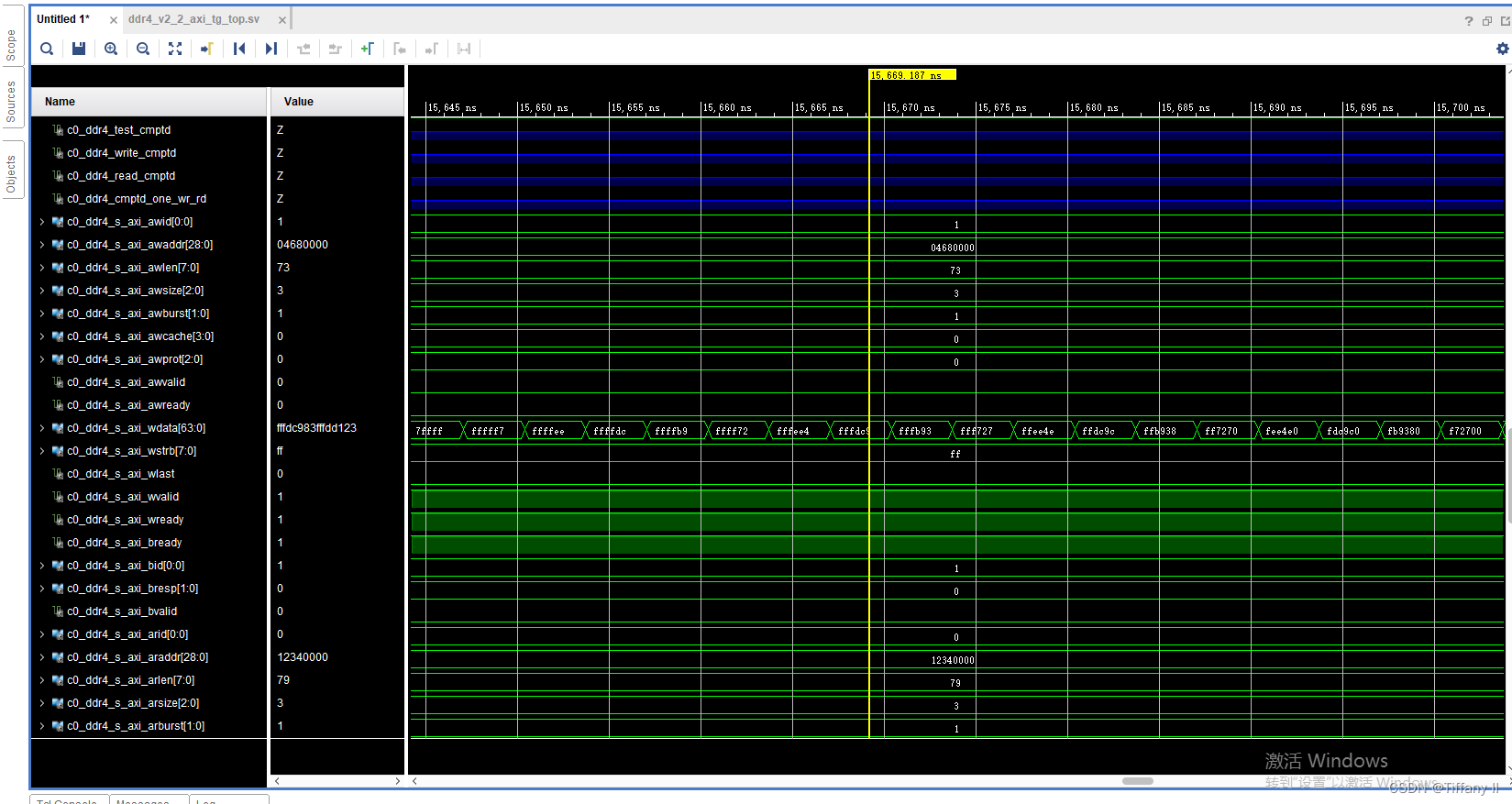

开发FPGA对DDR的驱动,首先需明确方案需求。这需求可能涉及简单数据缓存,或是复杂图像视频处理中的数据暂存等。目的明确后,便需着手选择或开发DDR控制器。若选用IP核,还需对IP核参数进行细致配置。这些参数涵盖数据宽度、存储容量等。配置不当,可能引发数据传输错误或资源浪费。

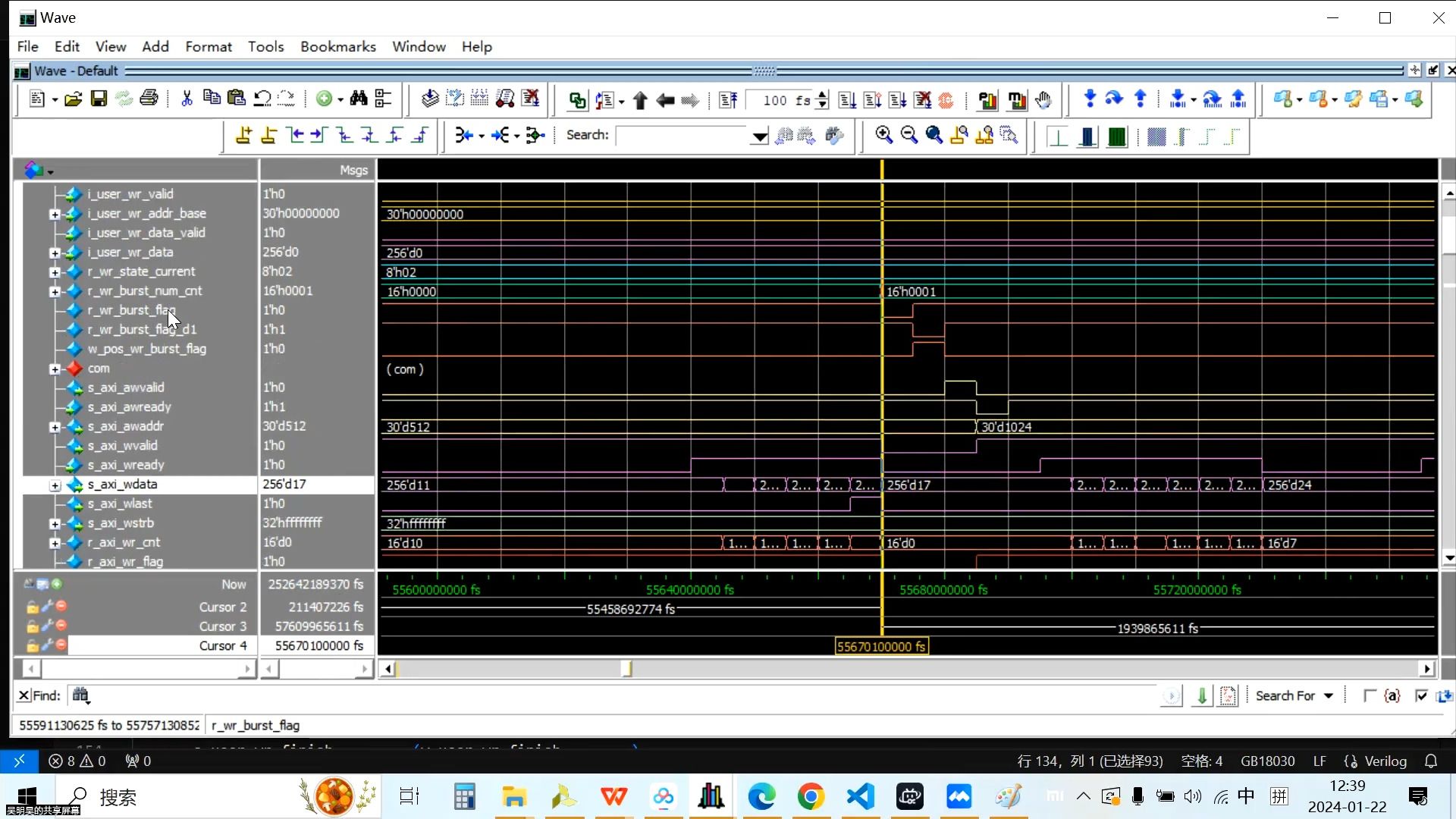

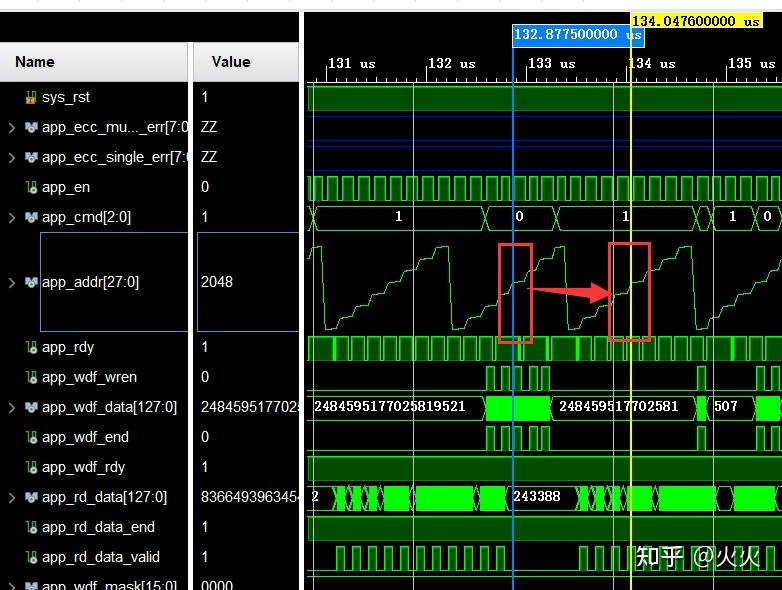

开发或配置完成后,测试阶段显得尤为关键。测试过程中,必须核实数据的读写是否准确无误。具体操作是,先写入已知数据,随后进行读取以验证其正确性。比如,可以先写入从0到100的连续数字,再读取检查是否与写入的一致。一旦发现错误,需从硬件连接和软件配置等多个角度进行排查。这一过程要求耐心细致,因为在这个复杂的驱动开发流程中,任何微小的疏忽都可能引发功能性的障碍。

关键性能指标

数据传输速率是DDR驱动的一个关键性能指标。这一指标直接影响着FPGA系统的整体吞吐效率。目前,DDR4的数据传输速率相较于DDR3有了明显的进步。若要实现更快的传输速度,信号的完整性便成为了关键考量。比如,信号的布线长度、布线层以及信号间的距离等因素,都会对信号完整性产生影响。

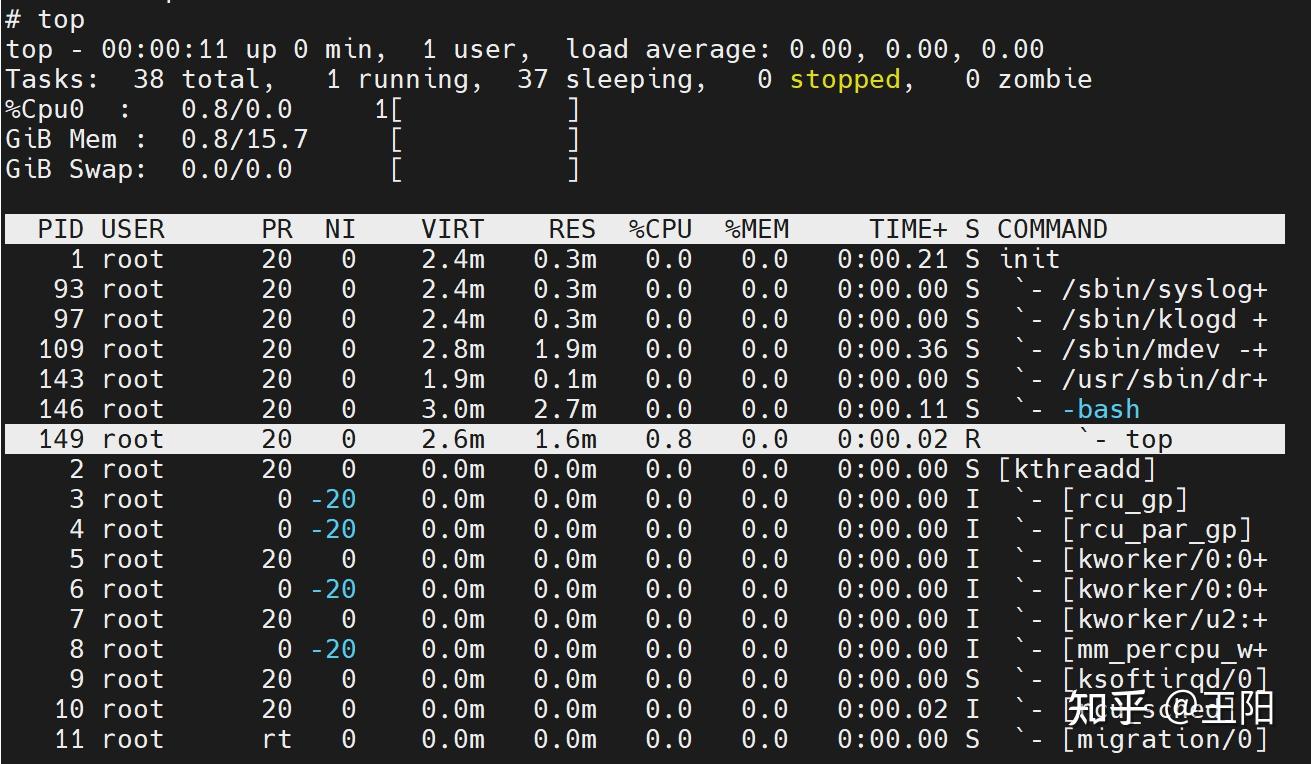

存储容量也是一个关键指标。它在不同应用场合的需求差异显著。比如,小型物联网设备可能仅需小容量DDR,而数据中心的大型服务器则需大容量DDR。在FPGA驱动DDR的过程中,我们必须根据实际需求来合理规划DDR的存储容量,并且要在存储容量、成本和功耗之间取得平衡。

常见问题

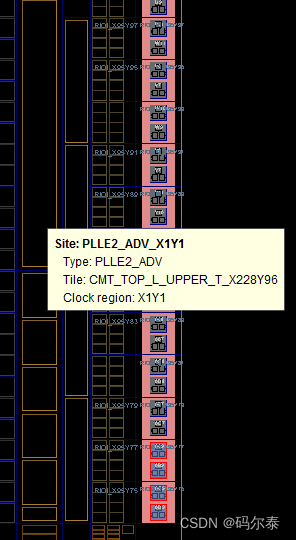

在FPGADDR驱动中,数据报错是个常见现象。它可能源于数据读写时的误码或丢失。这种情况往往是因为时钟信号的不稳定。若时钟偏移或抖动过于严重,便会引发数据传输错误。为解决这一问题,我们需采用高精度时钟源,并对时钟布线进行优化处理。

硬件连接不匹配是常见问题之一。比如,数据线连接顺序出错或地址线连接不完整。操作时,务必仔细参照DDR手册,确保硬件连接准确无误。硬件连接完毕后,还需仔细检查,以减少因连接问题引发的驱动故障。

优化方案

提升DDR性能的关键在于合理调整时序设置。通过调整读写数据的时序参数,能够增强数据传输的精确度和速度。比如,提前数据采样的时间点,能有效降低数据传输出错的可能性。此外,在软件层面,对DDR驱动代码的优化同样至关重要。运用高效算法来管理DDR的读写动作,有助于提升系统整体性能。

另一个改进措施是对硬件电路进行优化。比如,给DDR加入恰当的电源滤波电路,这样可以减少电源噪声对信号传输造成的干扰。另外,依照高速PCB的设计规范,对DDR的线路布局进行优化,以此降低信号之间的相互干扰,并提升信号的完整性。

实践案例

在图像处理项目里,我们得用FPGA来驱动DDR存储图像数据。最初设计时,传输速度不够,图像显示出现卡顿。经过检查,问题出在数据读写接口的时序设置不合理。调整了时序参数后,数据传输速率得到了提升。此外,为了增加存储空间,我们使用了更高密度的DDR芯片,并对硬件布局进行了重新规划。

还有一个高速数据采集项目,DDR在此项目中充当数据缓存的角色。起初,在硬件连接过程中,数据线之间的串扰引发了数据错误。经过对PCB设计中的布线进行重新规划,并实施数据纠错编码,我们成功解决了数据错误的问题,同时提升了数据传输的可靠性。

在进行FPGADDR驱动开发的过程中,大家是否遇到了一些独特的问题?欢迎大家在评论区积极留言讨论。同时,也希望大家能够点赞并分享这篇文章。