DDR(双倍数据速率)的正常运作,时序的安排至关重要。这一过程涉及众多信号在时间轴上的精确配合,直接影响到数据的准确读写等关键操作。接下来,我们将从几个角度对DDR的操作时序进行详细的分析。

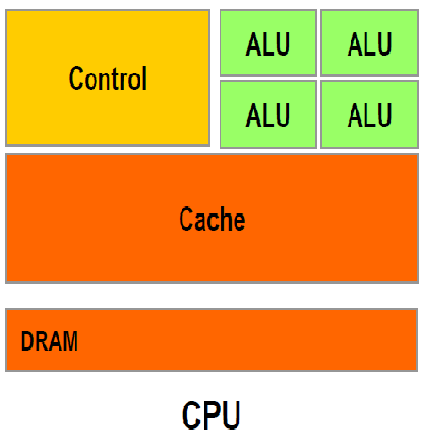

DDR对时钟信号非常依赖。它是操作时序的基准。在时钟周期内,DDR必须完成数据的输入输出等操作。比如,时钟的上升沿和下降沿都用于数据传输,这与单沿触发不同。双沿触发机制大大提升了数据传输效率,但对时钟信号的稳定性和精度要求更高。DDR设备中的时钟发生器和时钟分配网络必须精心设计,以确保时钟信号到达每个存储单元和逻辑电路时,能满足时序要求。

在实际应用中,计算机系统若出现时钟信号偏差较大的情况,DDR数据传输就会出错,甚至可能导致系统崩溃。因此,工程师在设计涉及DDR的硬件,如主板电路时,必须高度重视时钟信号的布线等因素。

地址信号的时序

地址信号在DDR的操作时序中扮演着至关重要的角色。首先,在读写过程中,地址信号总是先于数据信号出现,它的作用是告诉DDR模块需要操作的存储单元具体在哪里。其次,地址信号持续的时间长度也有严格的要求。如果持续时间太短,DDR可能无法及时识别出有效的地址,从而造成操作失败。以多任务处理的计算机系统为例,当CPU需要从DDR中迅速读取某个程序段时,精确的地址信号时序是确保快速获取正确数据的基础。

在实际的硬件设计中,CPU发出的地址信号,在经过总线传输至DDR模块的过程中,必须对信号延迟等各项因素进行精确计算。这样做是为了确保满足时序要求,避免因时序问题导致程序运行出现错误。

数据信号传输时序

数据信号的传输时机,正是DDR有效数据传输的关键。数据一旦准备就绪,便需遵循时钟信号的节拍进行传输。同时,还需关注数据建立与保持的时间。数据建立时间,即信号从到达DDR输入端口到稳定之前的时间段;保持时间,则是信号离开输入端口后保持稳定的状态时长。这两个时间段都是确保数据被DDR准确读取不可或缺的条件。

在一些高速数据采集系统中,DDR被用作存储大量采集数据。然而,一旦数据信号传输时序出现故障,采集到的数据就可能出错。这种情况会进一步影响到整个数据采集分析过程结果的准确性。

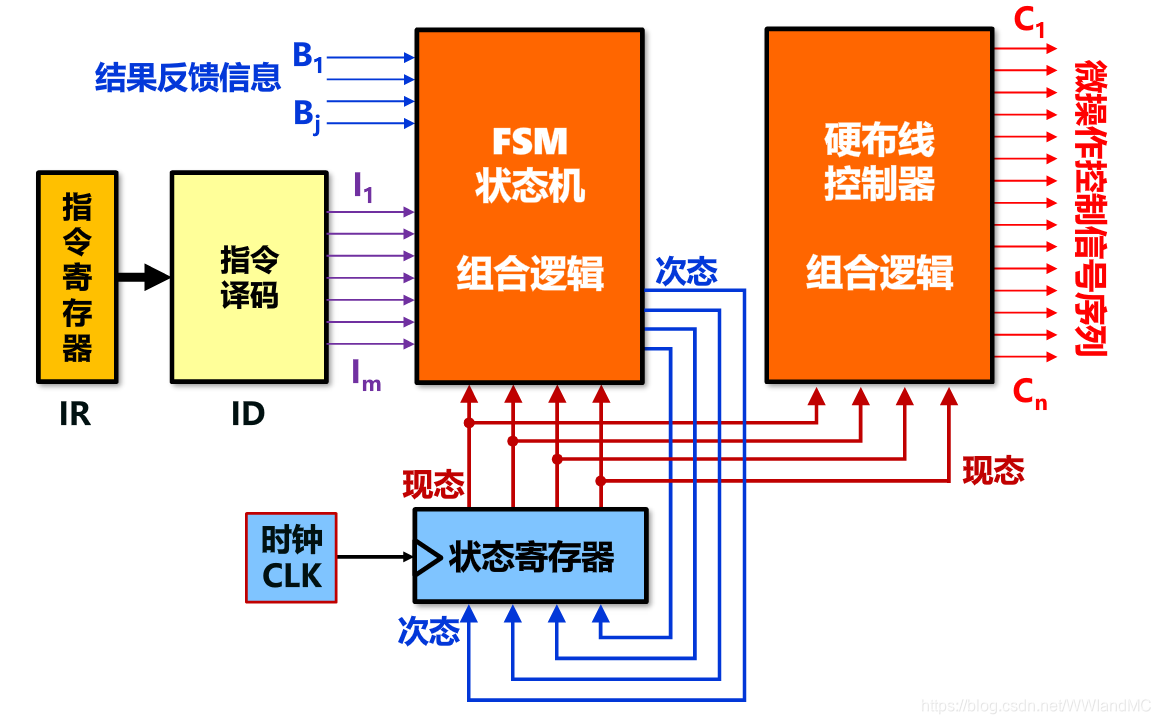

命令信号时序

命令信号对DDR模块的操作起到指引作用。比如,进行写命令和读命令时,每种命令都有其严格的时序规定。在发送写命令前,必须确保地址信号等关联信号已经就绪,之后才能发送命令。读命令的操作类似,而且命令的持续时间也有限制,必须保持固定。若命令信号提前或延迟发出,都可能干扰DDR的正常工作流程。

在实际的DDR芯片与控制器交互过程中,若控制器发出的命令信号的时序与DDR芯片的设计时序不一致,DDR芯片的读写操作将可能出现乱序或无效的情况。

预充电和刷新时序

DDR的正常性能依赖于预充电和刷新操作。预充电涉及调整位线电压至适宜水平,为后续操作做准备。这一过程遵循特定的时间顺序,需在读取或写入一定次数后及时执行。而刷新操作则是为了防止存储单元数据丢失,需定期对存储单元进行重新写入。刷新操作同样对时间间隔有严格规定。

长时间运行的服务器系统,若在预充电和刷新时序上出现问题,存储数据可能会出错。这种情况会影响服务器处理客户请求的能力。

不同模式下的时序差异

DDR具备多种工作模式,诸如不同的频率模式等。在这些模式下,操作时序各有不同。在低频模式下,对时序的要求相对较为宽松;而在高频模式下,对信号的时序要求则更为严格。这是因为高频模式下,信号在单位时间内变化更为频繁,对时间精度的要求也更高。

在挑选电子产品所需的DDR芯片时,需从实际应用出发,注意芯片在兼容模式下操作时序是否与产品电路设计及性能要求相吻合。若不相符,DDR芯片可能无法正常工作,甚至会导致设备整体性能大幅降低。

关于DDR操作时序的讲解,希望能给大家带来一些收获。大家在操作过程中,是否遇到过DDR相关难题?不妨在评论区分享你的经历。觉得内容有用的话,别忘了点赞和转发。