DDR(双倍数据率同步动态随机存储器)的正常运行,行列控制是其核心机制。这一机制对数据的读写和存储至关重要。本质上,行列控制就像DDR的指挥棒,它决定了数据在存储单元中的位置和提取方式。下面将对此进行详细说明。

基本概念理解

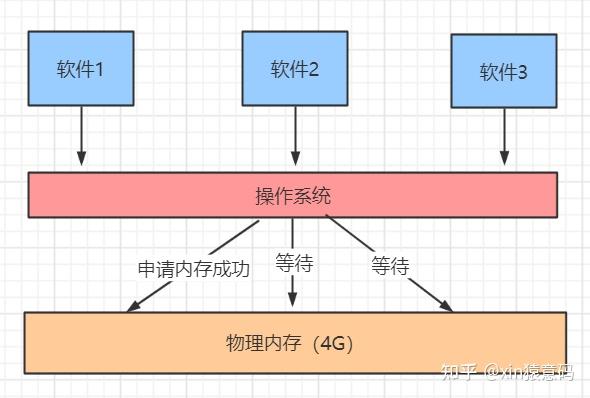

DDR的行列控制并不简单。首先,行地址和列地址是决定数据存储位置的关键因素。这就像地图上的横纵坐标一样。比如,如果我们把DDR比作一个庞大的仓库,那么行和列就如同货架的排数和层数。只有确定了行和列的坐标,我们才能精确地找到特定位置的数据。此外,随着DDR技术的发展,行列控制也在不断优化。以DDR4为例,它相较于DDR3,在行与列的数据定位精度和速度上都有了显著提升。

实际运行中,行列控制命令的发送频率和时序要求极为严格。这就像交响乐演奏时指挥的节拍一样,哪怕是一丁点的偏差,都可能使得结果与预期大相径庭。

行控制机制

行控制有其独特的操作机理。行激活是行列控制流程的初始步骤。行一旦被激活,相关数据便准备就绪,可供访问。比如在图像渲染环节,若需从DDR中提取特定图像的像素数据以供显示,首先激活包含这些像素数据的行,这是首要任务。

行预充电是关键的一环。当一行数据访问完毕后,它会对该行进行预充电,以便为接下来的行激活做好准备。这就像火车到站后,乘务员迅速清理车厢,为迎接下一批乘客做准备一样,是高效数据处理中不可或缺的一步。

列控制主要是在已确定的行的基础上,对具体数据进行定位。列地址选择电路会根据接收到的列地址信号,准确选取所需数据。打个比方,就好比确定了一本字典的某一页,那么列控制就如同在这一页中寻找特定的字。

而且,读与写操作各有其特性。写操作时,数据需依照列地址精准无误地存入相应存储单元;而读操作,则需通过列控制精确读取,同时确保不影响邻近数据的正常状态。

时序要求

DDR在行列控制上对时序的精确度要求非常高。写入数据时,时序需精确到每个时钟周期。一旦时序出现混乱,就好比在组装精密仪器时,零件安装的时间出现了错误,这样整个DDR的数据处理预期效果就无法实现。

此外,读取数据亦是如此。时序就好比火车的时刻表,若是延误或提前,便会引发数据读取错误,或导致所需数据无法准确获取。因此,必须设计一套DDR系统,对时序进行精确的控制。

与带宽的关系

行列控制与DDR带宽紧密相连。行列控制的高效运作,可以增强数据传输的带宽。一旦行与列能迅速且精确地定位,单位时间内传输的数据量就会增加。这就像调整交通信号灯,让道路上的车辆流动速度加快。

相反,一旦行列控制出现故障,带宽便会遭受严重打击。例如,若行预充电或列定位时间过长,数据传输速度便会减慢,DDR的整体性能将大幅下降。

故障排查与优化

遇到行列控制故障,必须进行彻底的检查。首先,要检查地址信号线路是否一切正常,比如确认行地址线是否存在虚焊或短路等问题。这个过程,就好比检查水管是否破裂或堵塞,是否会影响水流,同样至关重要。

若想实现优化,可以通过优化控制逻辑算法达成。比如,可以采用更智能的行列激活顺序,这样可以减少不必要的等待时间。这就像制定一个更合理的工作流程,目的是为了提升生产效率。

大家对DDR行列控制有何独到见解或实践体会?欢迎踊跃留言交流。如觉得本文对您有所帮助,请记得点赞并转发分享。