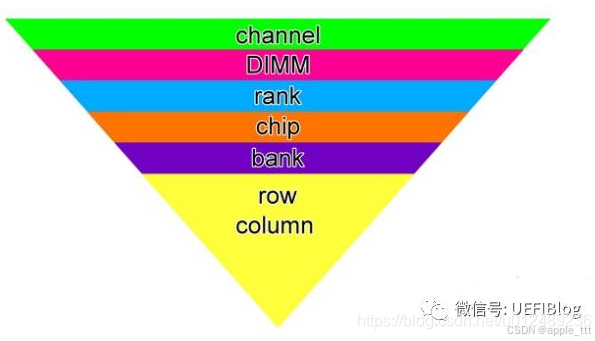

DDR,即双倍数据率同步动态随机存取存储器,其行列选择是内部数据读写的关键。这相当于在庞大的仓库中精确找到货物的位置,对DDR功能的发挥至关重要。

基本原理

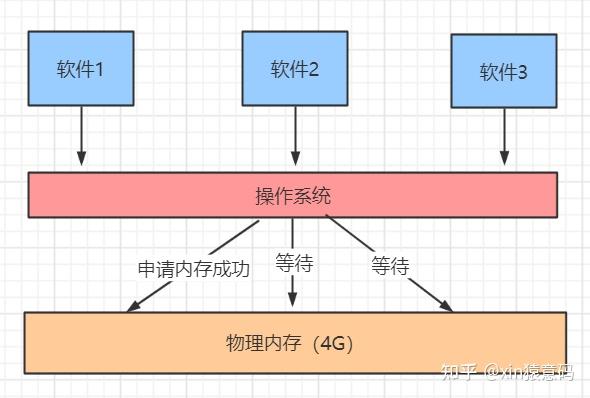

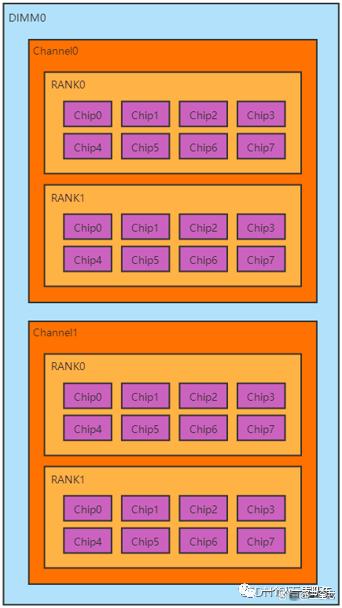

DDR为何需要行列选择,这与其存储结构密切相关。它宛如一个庞大的矩阵,行列交错定位了存储单元。从电路角度看,通过特定电路解码行列地址。这种设计在不占用过多线路资源的前提下,确保了数据的精准访问。这一原理在生产与设计过程中持续优化,旨在提升数据读写速度。尽管原理看似复杂,却是DDR高效运作的根本。若此原理出错,DDR的整体运作可能受影响。

在现实操作中,众多电脑的内存条设计都基于此原则。电脑需要从内存中读取数据,而这离不开DDR内部清晰的行列结构。这种逻辑电路的稳定运行,对电脑的整体性能有着至关重要的作用。

行选择

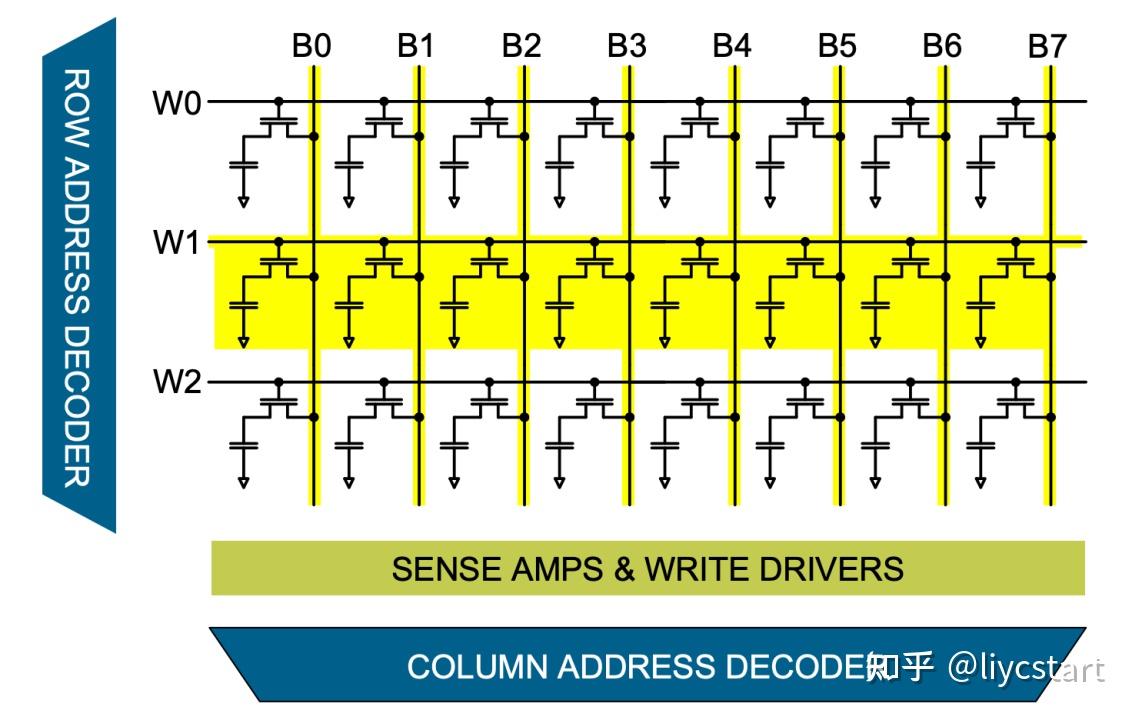

在DDR的工作机制中,行选择扮演着至关重要的角色。首先,它需要依据地址信息,从众多行中筛选出特定的那一行。这个过程涉及到了丰富的半导体电路知识。比如,要精确地激活对应的行线,就必须对信号进行精确操控。如果选错了行,即便后续的列选择正确,也无法获取到准确的数据。

设计电路板时,行选择的布线与芯片布局至关重要。不良的布局可能引发电容耦合等问题,进而影响行选择信号的精确度。随着技术的进步,行选择技术也在持续优化。我们的目标是实现更快速、更精准地选择需要操作的行。

正确地选择了行之后,紧接着便是列的选择。这一步骤是在已确定的行中,进一步确定具体存储单元所在的列。列选择本身就是一个复杂的过程,它需要依据特定的列地址来进行判断。从硬件的角度来看,列选择电路必须具备极高的稳定性。一旦列选择电路出现故障,即使行选择正确无误,数据也无法顺利传输到数据总线。

在实际的大规模生产过程中,确保不同内存颗粒的列选择功能保持一致,这无疑是一项挑战。众多厂商正积极努力,旨在解决这些问题,并以此提升产品的合格率。

行列选择的时间关系

行选择必须在列选择之前执行,两者在时间上有着固定的先后顺序。行选择操作需持续一定时长,之后才能进行列选择。这段时间的间隔必须精确把握。若时间处理不当,数据传递将无法按时达到准确度。特别是在高频DDR操作中,极小的时差都可能引发数据乱码等问题。

在设计高速内存系统过程中,工程师们必须关注行列选择时间关系的调整,这项工作至关重要。他们不仅要对硬件电路进行信号延迟的微调,而且往往还需软件算法的辅助,才能实现理想的性能。

影响行列选择的因素

外部环境对DDR的行列选择有影响。其中,温度是一个尤为重要的因素。温度过高或过低,都会导致半导体器件的性能发生改变,进而可能降低行列选择的准确性。此外,电磁干扰也在行列选择的过程中起着不良的作用。

在恶劣的工业环境中,使用搭载DDR存储的设备时,常常会遇到一些问题。以高温车间中的自动化设备为例,内存可能会因为高温而出现行列选择错误。为了减轻这些影响,这些设备通常会采用特殊设计,比如进行散热设计或电磁屏蔽。

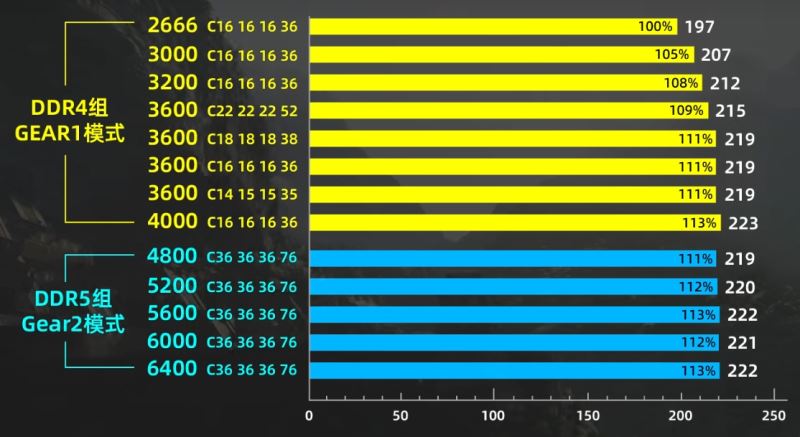

行列选择与性能提升

对DDR的行列选择动作进行优化,能显著提高性能。例如,通过改进行列选择的算法,可以缩短数据读取的时间。更精确的行列选择,意味着减少了对错误地址的访问,从而降低了能量消耗。从用户的使用体验来看,当电脑或设备读写DDR内存的速度提升时,整体响应性能也会得到增强。

在使用手机和电脑的过程中,我们常常期待程序能更快地响应。这其实与DDR的行列选择技术有着密切的联系。你有没有想过,手机为何会突然变得反应迟钝,这或许就是DDR行列选择出了问题。如果你觉得这篇文章对你有所启发,不妨点赞并分享,同时欢迎在评论区留言,一起探讨更多相关问题。