在电子电路设计领域,DDR布线尤为关键,尤其是其中的PinDelay,它是一个不容忽视的重要环节。PinDelay不仅关系到信号的完整性,更是决定整个DDR系统性能的关键因素。

DDR布线简述

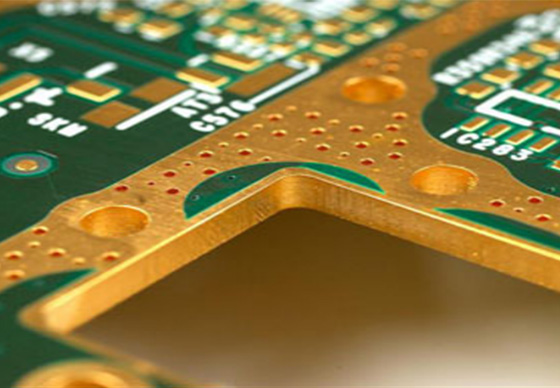

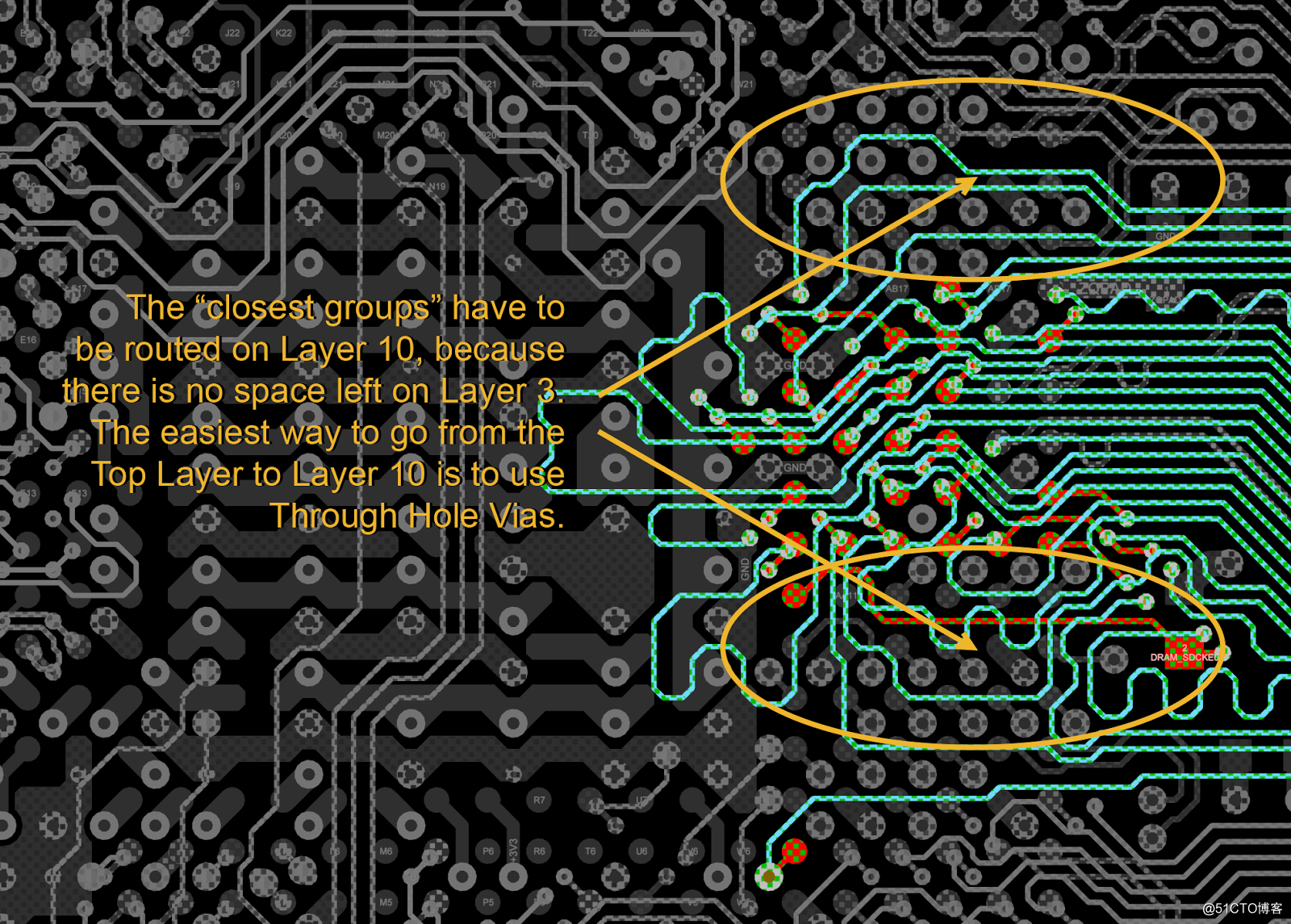

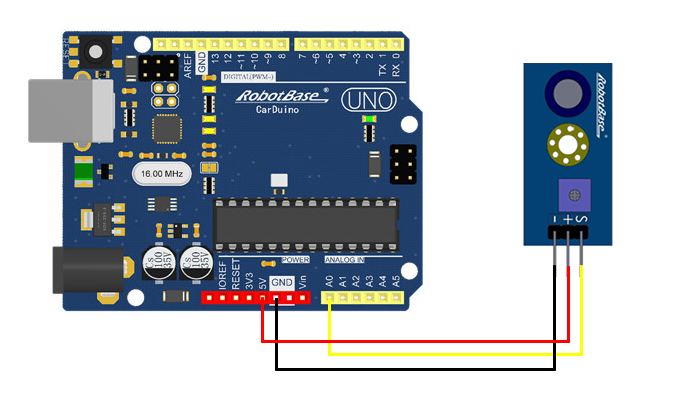

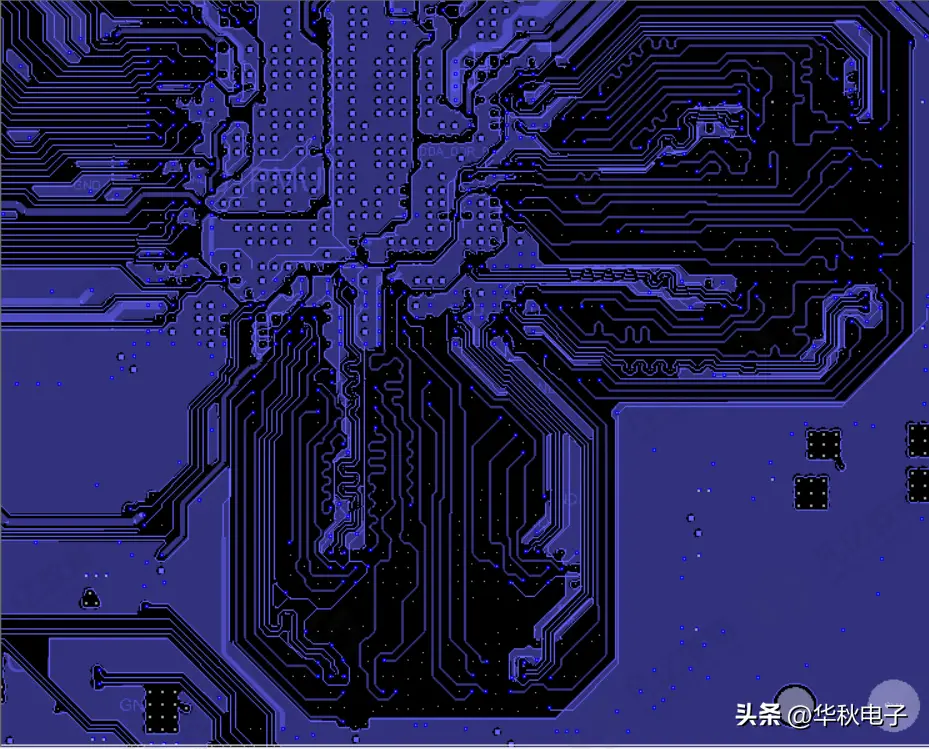

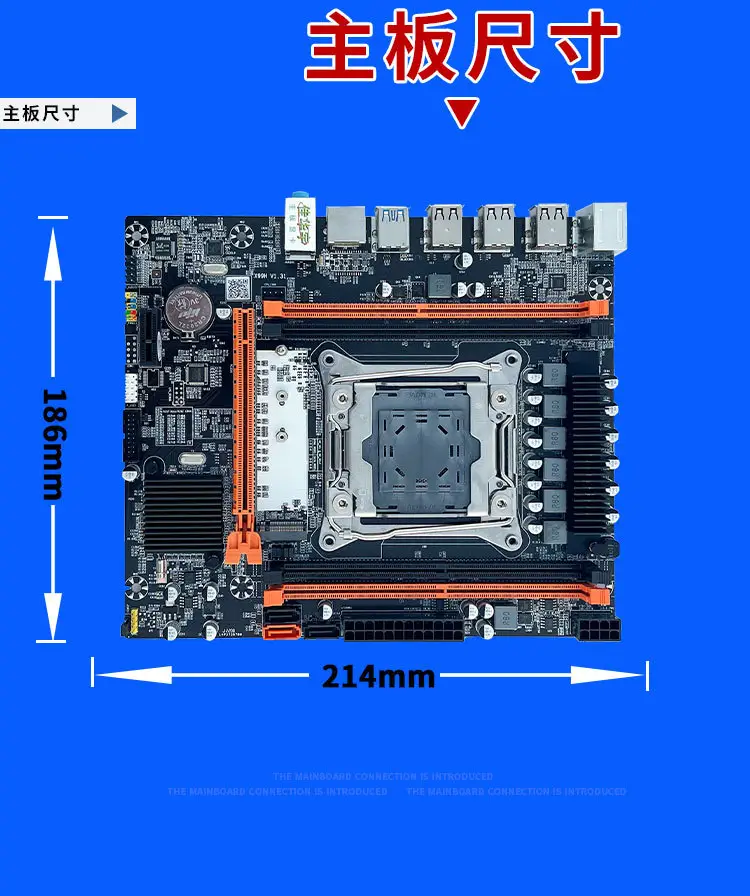

DDR的布线相当繁琐,需要连接许多电路元件。要想实现良好的DDR布线,必须在有限的空间里确保信号有效传输。若布局不合理,信号可能会相互干扰。实际上,不同版本的DDR布线要求各异,比如DDR3和DDR4就有显著的不同。在PCB设计阶段,若DDR布线混乱无序,后续的信号传输、读取和写入将面临诸多问题。此外,DDR布线的长度也有严格规定,过长或过短都会影响最终效果。这需要精确的计算和周密的规划,以确保信号能够稳定传输。

DDR布线的优劣直接影响着电子设备的整体性能。在当前一些高端计算机或服务器的设计中,DDR布线的效率更是直接决定了数据读写速度的快慢。一旦DDR布线质量不佳,计算机就可能出现死机、蓝屏等问题。

PinDelay的基本概念

PinDelay,从字面看,指的是引脚的延迟。它在DDR技术中扮演着至关重要的角色。每个引脚都如同信息的通道,一旦延迟发生,信号传输的节奏便会被打乱。在电路的实际应用中,由于加工工艺、材质等多重因素,每个引脚都可能存在微小的延迟。这种延迟不容忽视,尤其是在高速数据传输过程中,微小的延迟累积起来可能会引发严重问题。以笔记本电脑为例,DDR的PinDelay会影响到其开机速度和软件的启动速度。若延迟过高,系统启动可能会变得缓慢,软件运行也可能出现卡顿等问题,给用户带来不便。此外,高性能显卡中的DDR同样会受到PinDelay的影响,处理不当的话,渲染出图的时间会显著增加。

PinDelay并非神秘莫测,它并非不可控制。工程师们能借助先进的测量设备,准确获取其数值。这为后续的优化工作奠定了基础。然而,问题并非仅此而已,还有众多相关因素需要考虑。

影响PinDelay的因素

元件特性对PinDelay有着决定性的作用。不同芯片厂商生产的DDR芯片,其引脚延迟水平各异。这种差异可能与制造工艺的优劣有关。以老旧工艺为例,其引脚的电气性能不稳定,往往导致PinDelay较高。在批量生产前,必须对元件进行严格测试和筛选,以降低因元件问题引起的PinDelay。

电路板的布局对PinDelay影响极大。布局不合理会使信号传输路径拉长,进而增大PINDelay。例如,信号线路在电路板上被其他元件或布线阻挡,不得不绕道而行,这额外的距离自然会导致更多延迟。此外,若功率线路和信号线路布局过于密集,容易产生电磁干扰,干扰还会使PinDelay状况进一步恶化。对于一些空间紧凑的电子设备,内部空间有限,对布局要求极高,稍有不慎就会导致PinDelay增大。

PinDelay对DDR性能的危害

信号完整性受损,最直接的原因就是PinDelay。DDR系统对稳定的信号传输非常依赖,一旦信号传输因PinDelay而失去原有的规律,数据传输错误就可能出现。数据一旦出错,整个存储系统的可靠性就会受到损害。比如,在数据库服务器上,如果DDRPinDelay引发数据传输错误,可能会导致数据库中的数据出错或丢失,对企业来说,这可能是灾难性的后果。

性能的降低在所难免。以手机为例,PinDelay的存在会导致App加载速度减慢,多任务处理时的流畅度也会降低。这样一来,用户在使用手机时往往会感到手机运行缓慢,反应迟钝,这无疑大大影响了使用感受。此外,在某些工业控制设备中,若DDR的PinDelay超出正常水平,设备的控制精度便会下降,甚至可能失去设备运行的稳定性。

测量PinDelay的方法

时域反射仪,简称TDR,是一种常用的测量设备。它的工作原理是向DDR线路发射一个短暂的脉冲信号,接着通过检测反射回来的波来了解引脚和线路的电气特性。这样,我们就能计算出PinDelay的具体数值。然而,使用TDR时,技术人员必须掌握一定的操作技巧,比如准确调整脉冲的幅度和时间宽度。若设置不当,所获得的数据将无法保证准确性。

网络分析仪可用于测量PinDelay。它能测量并分析DDR布线的S参数。S参数能显现电路特性,从而帮助推算出PinDelay。然而,网络分析仪价格不菲,在小公司或简单项目中可能不会使用。不管怎样,精确测量是进行误差补偿和数据处理的关键。

如何减少PinDelay

电路板布局的优化至关重要。合理规划线路走向,缩短信号传输的距离,有助于减少PinDelay。举例来说,应将信号线路沿最短直线路径布置,避免曲折和迂回。同时,在布局过程中,还需充分考虑到功率线路与信号线路之间的距离,以降低电磁干扰对PinDelay的影响。

采用先进驱动技术不失为一个解决之道。比如,某些新型的DDR驱动技术能够在信号驱动阶段就有效补偿PinDelay。这样一来,在信号传输开始前,就能对延迟进行一定程度的校正,显著降低了PinDelay对整个传输线路的影响。然而,采用这些先进技术通常会增加成本,这就要求我们在成本与性能之间做出权衡。

这篇文章旨在让你对DDR布线中的PinDelay有更深入的认识。我想问问,你在实际电路设计或是电子设备的使用过程中,是否遇到过DDR布线相关的问题?欢迎留下你的评论,点个赞,并将这篇文章分享出去。