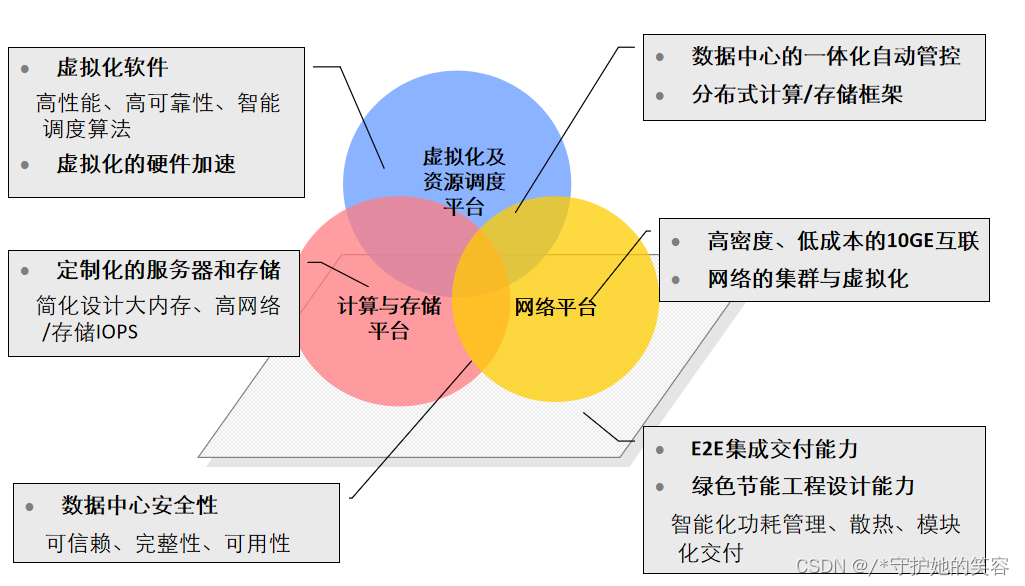

DDR(双倍速率同步动态随机存储器)的布局对硬件系统的性能起着决定性的作用。这并非仅仅是线路的连接,它还牵涉到众多设计规则和电气性能的考量,是一项技术性很强的工作。接下来,我将从多个关键点对这些方面进行详细解析。

DDR的基本概念

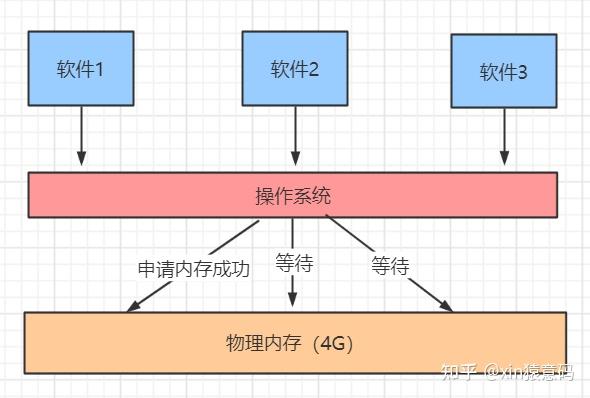

DDR,这种在现代电子设备中普遍应用的内存技术,其运作原理值得我们深入探究。DDR的读写操作能在时钟的上升和下降两个阶段同时进行数据传输,这一特点区别于传统内存。正是这种独特的工作模式,显著提升了数据传输的速度。对于DDR的布局而言,掌握这些基本概念至关重要。此外,DDR还分为多个世代,如DDR3、DDR4等,不同世代在传输速度和存储容量上各有千秋。一般来说,新世代的DDR速度更快,容量也更大。

DDR的物理结构较为复杂,主要由众多存储单元构成,这些单元通过电路相互连接。在进行布局时,我们必须明确每个部分的功能以及它们之间的连接方式。若对此缺乏了解,便可能产生连线错误,或是导致电气性能不理想。

布局的基本规则

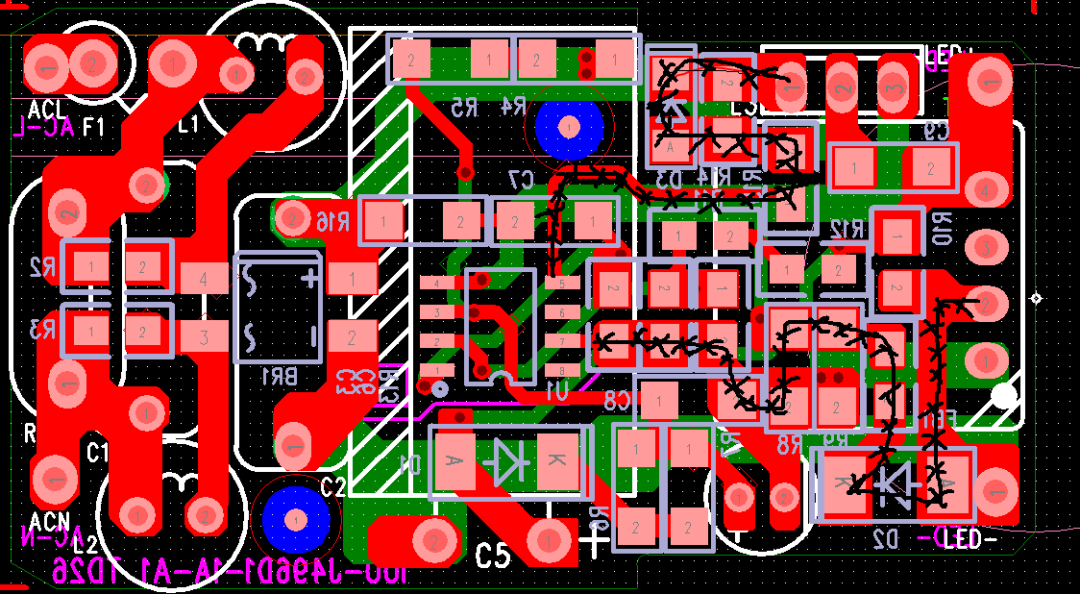

DDR的布局设计,首要关注的是信号的完整性。为此,在布线阶段,需努力缩短信号传输的路径,以降低信号在传输中的衰减。要知道,信号在长距离传输或遇到障碍时,会自然衰减。若不进行有效控制,便可能引发数据传输错误。此外,同类信号的走线长度也应尽量保持一致,以防止因信号传输时延而产生问题。

电源和地的规划至关重要。稳定的电源是DDR正常运行的必要条件。在电路布局时,必须注意电源线路的线宽,确保其能够输送足够的电流。同时,地的接地必须良好,以防止地弹问题的发生。试想,若电源和地不稳定,就如同汽车在坎坷不平的道路上行驶,DDR的运行必然会受到干扰。

传输线的考量

DDR布局中,传输线扮演着至关重要的角色。而确保传输线特性阻抗的匹配,则是一项至关重要的工作。若特性阻抗不匹配,就会产生反射,这就像球击中墙壁后反弹回来一样。数据信号在传输线中反复穿梭,导致信号紊乱。因此,我们需要通过合理布线,例如使用微带线或带状线等不同布线形式,来调节特性阻抗。

传输线之间的距离同样不可忽视。距离若过窄,信号就可能发生干扰。这就像在狭小的空间里,人们容易相互干扰,相邻的传输线若距离过近,也会相互影响,原本清晰的信号就会变得混乱不堪。

布线的技巧

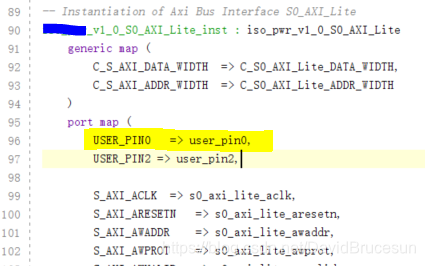

布线在DDR布局中占据关键位置。分层布线是一种实用的方法。通过将不同类型的信号分别安置在不同的层次,能显著降低信号间的相互干扰。例如,将数据信号和控制信号分开布置,就能有效防止数据被控制信号所干扰。

还有一点布线上的特别要求,那就是DDR的时钟信号,它是DDR运作的节奏所在。因此,时钟信号的走线必须力求短而直,减少过多的弯曲,这样才能确保信号的精确无误。一旦时钟信号出现误差,DDR的运作就会如同音乐失去节奏,变得混乱不堪。

噪声的处理

噪声对DDR来说是个大问题。在布置时,需注意识别可能出现的各种噪声来源。例如,周围其他电子元件可能引发的电磁干扰,也可能成为噪声的源头。对此,我们可以采取增加屏蔽措施来降低噪声。这就像给婴儿戴上柔软的耳塞,以隔绝外界噪音一样,为DDR设计一个屏蔽罩,使其能在相对安静的环境中运行。

干扰电源的纹波噪声不容小觑。采用恰当的滤波电路能有效降低这种干扰。若不加以处理,电源纹波噪声犹如湖面泛起的小波纹,会扰乱DDR信号的稳定。

测试与优化

完成DDR布局后,测试显得尤为重要。我们可以借助多种测试工具,比如示波器等,对信号质量进行检测。测试过程中,能揭示布局中的一些潜在问题,诸如细微的信号干扰或是过大的时延等问题。

测试时若发现问题,便需对布局进行优化。优化并非只是对某一部分进行简单调整,而是要全面考虑整个布局。比如,可能只是对一条走线的位置进行微调,但这实际上是对整体电气性能进行持续考量的过程。

各位读者,我想请教一下,在你们进行DDR布局时,遇到过什么最大的难题?期待大家的热情参与和评论。若觉得这篇文章对您有所帮助,请别忘了点赞和转发。