DDR(双倍数据速率)在电子设计行业中占据着核心位置。Allegro作为一款普及的设计软件,其规则配置对DDR的稳定运行和性能提升至关重要。以下将分多个角度对DDR的Allegro规则进行深入探讨。

元件布局规则

DDR布局下,元件的布局相当重要。首先,DDR芯片与控制器芯片应尽量放置在相近位置。这是因为它们之间的数据交流十分频繁,若距离太远,信号传输的延迟就会加大。比如在高速数据处理电路板上,这可能会导致数据读写出现错误。其次,元件的布局还需考虑布线的便利性,力求减少布线时的交叉和迂回,这样做有利于提升信号的完整性。

设计时必须注意散热因素。DDR芯片在运作过程中会产生热量,若布局不当,热量无法有效散去,便可能造成芯片性能的降低。比如,若把DDR芯片安置在散热条件不佳的狭小空间中,经过长时间的工作,由于热量的积聚,其运行频率可能不得不被强制下调,以确保系统的稳定运行。

布线规则

DDR布线需遵循线长匹配原则。在布设DDR的数据与地址信号时,信号需同步抵达接收端。为此,各数据线和地址线的长度差距需严格限制在极小的范围内。例如,在高端服务器主板的设计中,若线长差异过大,便可能引发数据读写至错误地址的问题。

此外,布线的间隔规范也需注意。不同信号间的间隔必须符合一定的电学标准,这样才能避免信号间的相互干扰。以高密度PCB设计为例,若布线间隔过窄,一条信号线上的信号波动便可能干扰邻近信号线的数据传输,从而导致信号传输出错。

电源规则

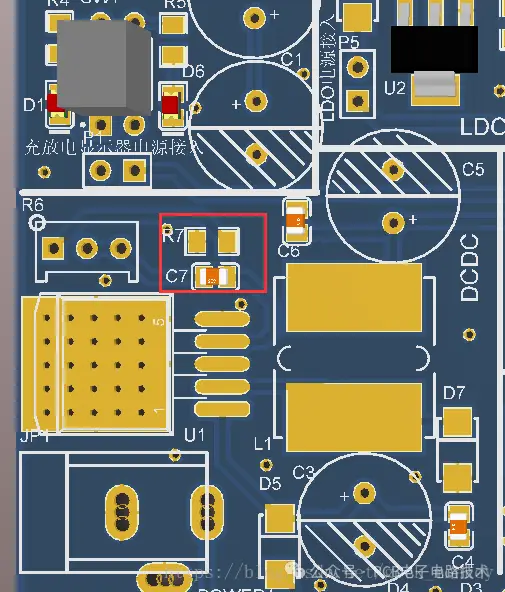

电源完整性对DDR的正常运作至关重要。首先,DDR芯片的电源端需要配备足够的去耦电容,以有效滤除电源噪声。若去耦电容数量不够,电源噪声便可能干扰芯片内部逻辑电路的稳定运行。以含有多个DDR芯片的系统为例,电源噪声还可能破坏数据的一致性。

电源层与地层的布局极为关键。合理的电源层与地层设计,能确保电源供应稳定,并形成优质的信号参考面。在众多复杂的电子设备中,若电源层与地层规划不当,很可能会引发电源波动剧烈,进而影响DDR的读写效率。

时序规则

DDR的时序规则对数据读取和写入的准确性有着重要影响。首先,时钟信号的处理至关重要,它必须精确无误地传输至每个DDR芯片单元。以高速数据处理电路为例,即便时钟偏差仅有几皮秒,也可能导致数据在错误的时间被采集。

另一方面,还需关注数据信号与时钟信号之间的时序映射关系。数据信号需在时钟信号规定的有效时间内抵达接收端,否则数据传输将出现错误。在实际设计过程中,对时序的调整常常需要综合考虑众多因素,并通过反复优化来实现。

信号完整性规则

信号反射是个值得关注的问题。信号在传输过程中,若遇到阻抗不匹配,就会产生反射。以PCB板布线为例,若其特性阻抗与DDR芯片的输入输出阻抗不匹配,反射的信号就会降低原有信号质量,进而引发数据传输错误。

同时,串扰会对信号完整性带来损害。这种损害源于临近信号线之间的电磁场相互影响。在PCB布线复杂的情境中,要减少串扰,必须合理设计信号线路,并选用恰当的间距以及屏蔽手段。

约束规则管理

在Allegro设计环境中,对约束规则的设置与管理需十分谨慎。首先,需将硬件设计中的具体需求,如DDR的带宽要求等性能指标,精确地转换为可配置的约束规则。比如,这些性能要求需被转化为布线宽度、间距等具体的约束条件。

此外,实时监控与调整约束规则同样关键。随着设计阶段的深入或是方案的变动,我们或许需要针对先前制定的约束规则进行相应的调整和优化,以确保它们能够满足新的设计需求。

欢迎各位在评论区分享关于DDRAllegro规则的个人见解或宝贵经验。若您觉得这篇文章对您有所帮助,请不要吝啬您的点赞与转发。我想请教大家,在具体的工作实践中,你们是否遇到过DDRAllegro规则方面的难题?