在电子系统领域,ARM外接DDR技术扮演着至关重要的角色。它关乎ARM系统性能的提升,以及存储空间的扩展等多方面的重要事宜。

适配性探讨

ARM外接DDR时,适配性是最重要的考虑点。不同的ARM架构对DDR的需求各不相同。在频率上,某些ARM架构仅能适配特定频率范围的DDR,超出这个范围系统可能会出现不稳定现象。以某款ARM芯片为例,其官方文档中明确说明了最佳的DDR频率适配区间。此外,DDR的容量适配也有其讲究。有些ARM设备因设计原因,只能接入特定容量范围的DDR。

工程师在选择型号时需投入大量时间进行深入研究和实际测试。若选型不当,可能导致系统整体瘫痪,这不仅会增加成本,还会延误项目进度。

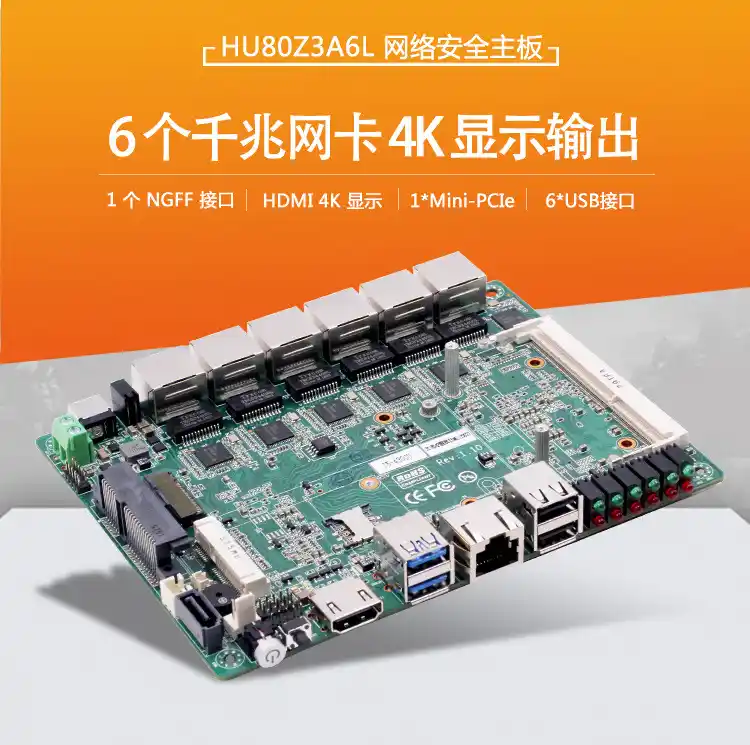

布线要点

布线对ARM外接DDR的稳定性极为关键。首先,信号完整性必须得到保障。在布线过程中,DDR信号的走线长度要妥善处理。走线过长会引起信号延迟,进而影响数据传输的精确度。特别是在多层板设计中,每一层的信号线走向都需要进行合理的规划。

此外,电源的完整性也是关键,DDR对电源的供应有较高的要求。布线时必须保证电源线的宽度足够,同时还要尽量降低电源线的电感。若电源布线不当,可能会导致电压波动,进而引发DDR读写错误。

时序调整

时序对ARM与DDR间的数据交互影响深远。在ARM启动阶段,DDR的时序初始化尤为关键。这一过程就好比是搭建沟通的桥梁。只有确立了正确的时序,才能确保数据的读写有序进行。比如,在执行首个读写指令前,DDR需按照特定时序来准备,这样才能告知何时可以开始操作。

系统运行时,环境变化等因素可能导致需进行动态时序调整。这是因为,在各异的工作频率和负载状况下,DDR的性能波动程度各异,故需适时调整时序以适应。

数据完整性验证

为确保ARM与DDR间数据传输的精确性,数据完整性的核实至关重要。这需要硬件监测手段的支持,例如,特定的监测电路能捕捉读写过程中的错误信号。以DDR存储数据为例,若出现奇偶校验错误,监测电路便能及时察觉。

此外,还有软件方面的验证工作。在系统软件中,可以编写程序对输入和输出的数据进行核对。如果发现数据存在差异,便可以采取适当的措施进行修复。

ARM外接DDR的系统里,功耗管理是绝不可忽视的。DDR在运行时确实会消耗不少电量。从硬件层面讲,我们可以挑选低功耗的DDR芯片。比如,有些DDR芯片运用了先进的工艺技术,它们在保证性能的同时,还能有效减少功耗。

系统在软件层面能够根据运行状态的不同,对DDR的工作频率和电压进行调整。比如,在负载较低时,降低DDR的工作频率和电压,这样既可以降低功耗,同时还能延长系统的整体续航时间。

升级与维护

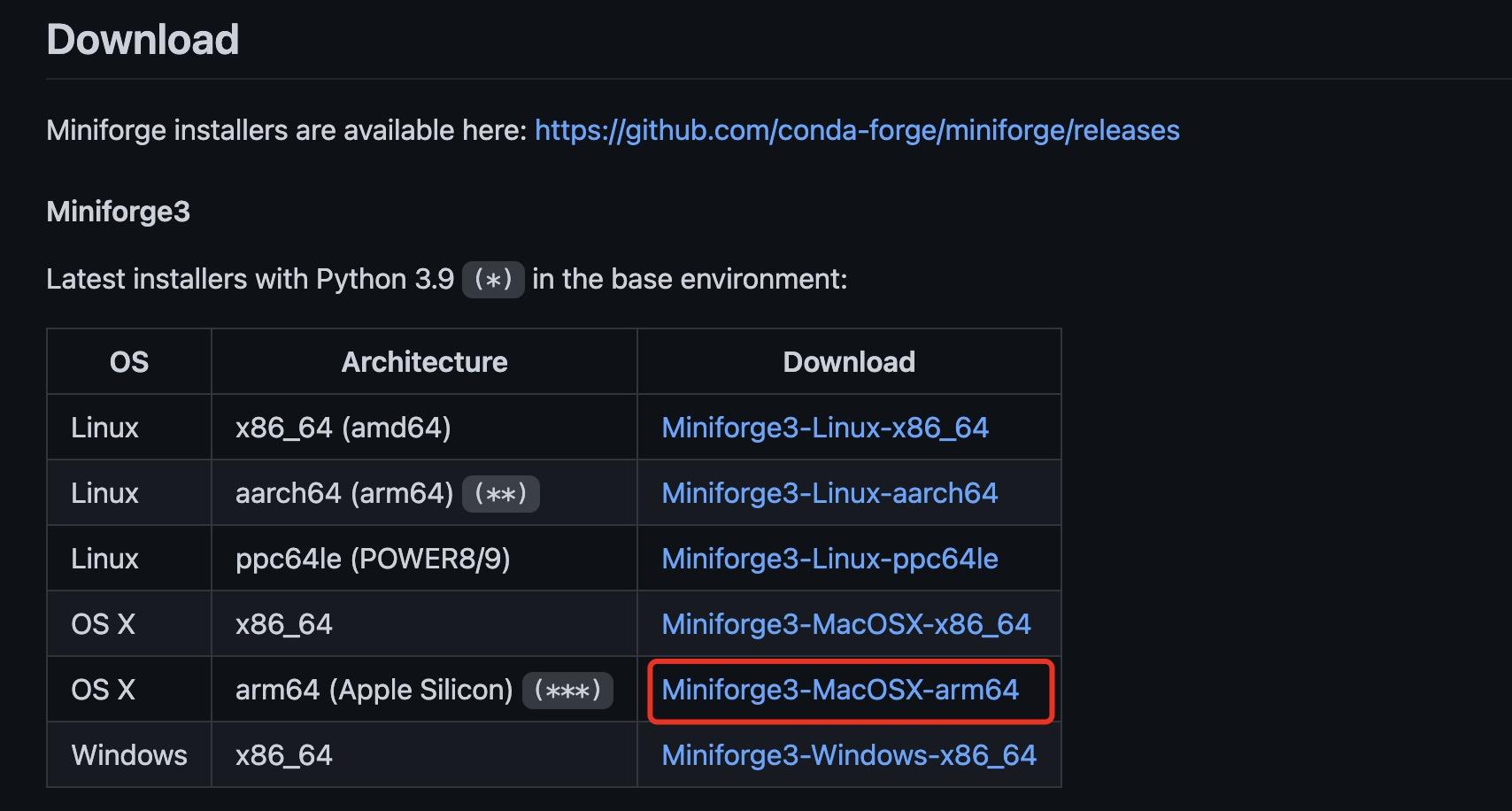

技术不断进步,DDR将迎来新的版本,ARM与DDR的连接升级变得不可或缺。在这一升级过程中,兼容性问题不容忽视。我们必须确保新版本的DDR与ARM的接口能够相容。同时,软件层面也要确保系统能够顺畅地驱动这些新的DDR设备。

日常维护同样重要。我们需要定期对DDR进行体检,比如运用专门的工具来检测DDR的内存健康状况。这样做有助于及早发现潜在问题,从而预防数据丢失带来的严重后果。

最后有个问题想和大家探讨,那就是在你们进行ARM外接DDR的过程中,最大的难题究竟是什么?欢迎大家在评论区交流讨论,同时也很期待大家能对这篇文章给予点赞和转发支持。