DDR(双倍数据速率)的工作时序虽然复杂,却至关重要。这一概念主要关注内存模块与其他部件在交互数据时信号的时序和参数设置。这些因素对整个系统的性能和稳定性有着决定性的影响。

读时序

DDR的读时序里,最关键的是tRCD,即行地址选通潜伏期。它影响从发出行地址到读取数据的时间。这个时间要适中,太短会导致数据读取错误,过长又会影响性能。比如,在高速计算机中,如果tRCD设置不正确,可能会导致画面卡顿或程序反应慢。还有另一个重要参数tCL,即列地址选通潜伏期。它同样影响数据读取,与内存芯片内部处理速度密切相关。

在实际使用中,不同版本的DDR对读时序的要求各有不同。以DDR3和DDR4为例,它们在tRCD和tCL的数值上有着显著的差别。DDR3的tRCD和tCL时间较长,而DDR4由于技术的进步,能够设定更短的时间,进而实现更快速的数据读取。对这些参数的优化和调整,对于提高系统性能是至关重要的。

在DDR的写时序中,tWP扮演着至关重要的角色,它指的是写保护时间。这个时间是为了在写入操作完成后,保证数据能够被准确存储,并且内存能够保持稳定状态。一旦tWP设置得太短,就可能会引发数据写入不完整或者数据损坏的问题,这在数据存储过程中可是极为严重的错误。举例来说,在数据库的写入操作中,错误的tWP设置可能会导致新写入的数据丢失或者出现混乱。

tWR指的是写入恢复时间,它决定了写入操作后多久才能进行下一次操作。若不按照正确的tWR执行,尤其在多线程处理频繁写入任务时,很容易导致内存冲突或数据错误,进而可能引发系统崩溃或数据混乱。

时钟信号时序

在DDR操作中,时钟信号至关重要,其中时钟周期tCK扮演着核心角色。它决定了数据传输周期的基本节奏,就如同乐队指挥手中的指挥棒。一旦tCK不稳定或设置不当,数据传输将陷入混乱。在高频运行的计算机系统中,一个精确的tCK能确保各组件间协调无间,实现数据交互。

时钟信号的上升沿与下降沿均用于数据传输,正是这一特性赋予了DDR双倍数据速率。然而,这也对时钟信号的品质及与其他信号的同步提出了严格的要求。任何微小的偏差,都可能导致数据在上升沿或下降沿传输时发生错误。

预充电时序

预充电操作对于DDR来说至关重要,它涉及到一个关键参数——tRP。这个参数指的是从预充电命令发出到下一个行激活命令执行之间的等待时间。只有设置得当的tRP,才能保证预充电操作能够完全发挥作用,从而不会干扰后续的行访问操作。以内存资源频繁切换使用的场景为例,如果tRP设置不当,内存的访问速度将会变慢,效率也会降低。

tRAS是与预充电相关的另一个时序参数,它表示从行有效状态过渡到预充电状态的时间。这一时间间隔对于一行数据的使用周期至关重要。如果不按规范设置tRAS,比如在频繁切换访问不同行数据的程序中,就会造成数据读写操作的显著延迟。

时序参数调整

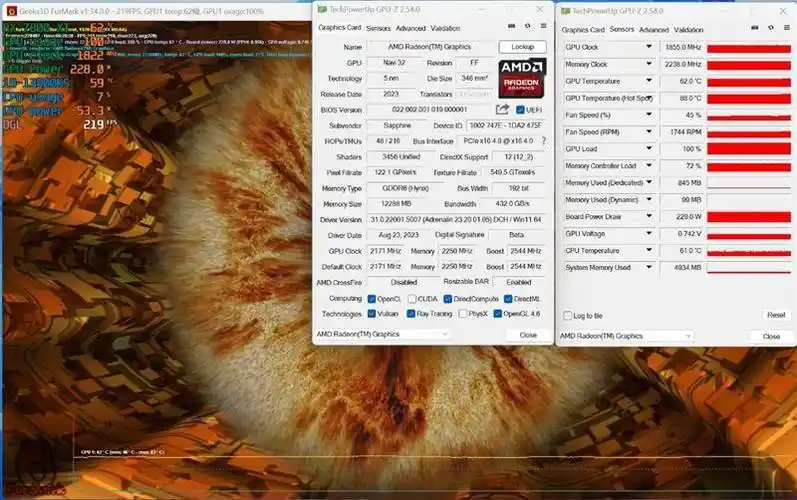

调整DDR的工作时序需考虑诸多要素。首先,硬件的兼容性是关键,比如不同品牌和型号的DDR内存与主板间,它们的时序兼容性各不相同。以高端主板为例,它们可能更擅长支持低时序的DDR4内存,而与老旧的DDR3内存搭配时,则可能需要调整时序以实现稳定的性能表现。

另一方面,依据实际应用需求来看,比如在游戏场景中,必须确保数据传输的时序得到优化,这样才能实现高帧率和流畅的画面效果。相对地,在服务器场景中,数据的准确性和稳定性显得更为重要。因此,在调整时序时,我们更要关注tWP和tWR等写时序参数,以免数据出现错误。

时序对系统性能影响

DDR的工作时序对系统性能至关重要。合理配置时序参数,系统便能充分发挥内存的最大效能。以多任务处理为例,优异的DDR时序能让任务快速读写数据,缩短等待时间,进而提高整体运行效率。这就像一个高效运行的物流系统,各个环节井然有序。

当时序参数出现异常,系统性能会大幅下滑。这时,我们可能会遇到设备卡顿、无法正常启动等问题。在如今这个对高性能计算需求不断上升的时代,DDR的工作时序若未正确设定,即便硬件配置再怎么先进,也难以发挥出其应有的强大性能。

我已对DDR的工作时序进行了详尽的剖析。在理解DDR的工作时序或进行相关设置时,你是否遇到了什么特别的问题?期待大家的积极讨论与互动。若觉得这篇文章对你有帮助,不妨点赞并分享!