DDR,即双倍速率同步动态随机存储器,其硬件构造构成了计算机存储系统的核心。简言之,DDR具备一些独有的结构特性,能够实现数据读写的高效进行。

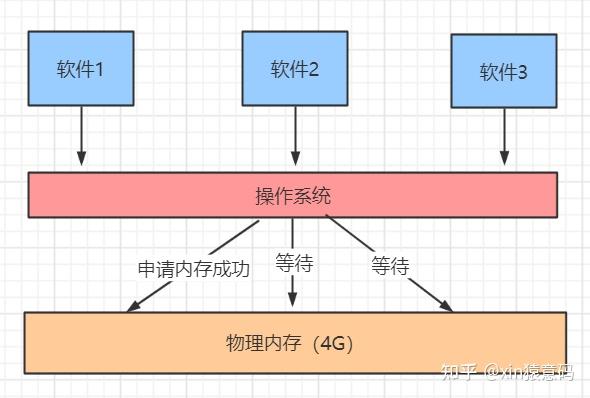

存储单元阵列构成了DDR硬件结构的核心。其中容纳了众多存储单元,它们以矩阵形式排列。每个单元均能存储一定数量的比特数据。这些单元是数据存储的最终归宿。就好比一座庞大的仓库,每个小格子代表一个存储单元。在计算机实际运行过程中,无论是程序代码还是运行中的数据,大部分都存储于此。此外,阵列的大小直接决定了DDR的存储容量,尺寸越大,存储容量也就越大。

存储单元阵列并非孤立存在,它必须与其它部分紧密配合,才能实现高效的数据读写操作。地址线将各个存储单元串联起来,就好比城市中的街道地址,让控制器能够精确地定位到所需访问的存储单元。

行地址与列地址

在DDR中,行地址和列地址对于数据的定位至关重要。行地址如同一个大区域的界限。DDR在运作时,首先要明确行地址。一旦行地址确定,就能锁定一组存储单元。而列地址则在此基础上进一步细分,能够精确地找到行内的特定存储单元。

在实际操作中,每当计算机需要数据,控制器首先会发送行地址,以此开启一整行的存储单元,这个过程在DDR中速度极快。紧接着,控制器会发送列地址,精确锁定所需单元。这种设计既提升了效率,又简化了控制流程。若直接定位单一单元,过程将会相当复杂。

数据输入输出接口

数据输入输出接口主要承担着DDR与外界数据交换的任务。这种数据传输过程是相当迅速的。数据会依照既定的协议,通过接口进入或离开DDR。这个过程可以比作一座桥梁。对于计算机系统而言,一个性能卓越的数据接口能够高效地将数据从DDR传输至处理器等设备。

接口的带宽影响着数据传输的最高速度。若带宽不足,即便DDR内部运行速度极快,数据也无法迅速从DDR移至所需位置。在实际应用中,接口的设计需依据整个计算机系统的具体需求来精心定制。

内部控制电路

内部控制电路在DDR硬件结构中扮演着调控者的角色。它承担着众多职责,例如管理字线和位线等。字线如同开启存储单元大门的钥匙,而位线则负责数据的传输。内部控制电路负责协调这些线路的运作。

它能接收并执行各种外部指令,包括读写指令等。比如,当电脑发出写指令,内部控制电路便会协调各个部件,确保在恰当的时刻将数据写入存储单元阵列。若缺少这一稳定的内部控制电路,DDR系统将无法正常运行。

时钟信号

时钟信号,它犹如DDR硬件结构的节奏指挥官。DDR,这种同步存储器,它的运作离不开时钟信号的协调。时钟信号,它周期性地跳动,而在每一个时钟周期中,DDR都会执行一系列规定动作,比如数据的读取或是写入。

时钟信号的频率高低对DDR的性能有着直接影响。频率越高,DDR在相同时间内能完成的数据传输和操作就越多。然而,频率过高可能导致信号完整性等问题。因此,在实际应用中,我们需要依据DDR的硬件设计和与其他部件的兼容性来选择恰当的时钟频率。

电源管理模块

电源管理模块负责保障DDR稳定运行的动力供应。它必须为各个部件供应恒定的电压和电流。这些部件的工作电压区间通常极为狭窄,因此电源管理模块必须确保输出的电源稳定可靠。

电源管理一旦出现问题,电压波动过大时,DDR便可能产生错误数据或数据丢失。而一个优秀的电源管理模块,就如同一位守护天使,默默守护着DDR的稳定运行。

在掌握了DDR硬件结构的这些关键点之后,你是否对DDR硬件结构未来的创新趋势有所思考?不妨在评论区发表你的看法,同时,也欢迎你为这篇文章点赞并转发。